## حقيبة تعليمية

# بعنوان: مكونات و دوائر الكترونية

### إعداد

التدريسي الرئيسي: م.م دينا جمال جبار التدريسي الثانوي: م.د سيف محمد براء

2023 - 2022

### المقدمة

يتسم البرنامج التعليمي لمقرر الاجهزة والدوائر الالكترونية بالتدريس باللغة الانكليزية لمدة ثلاثون اسبوعا بواقع ساعتين نظري وثلاث ساعات عملي اسبوعيا يتم تدريس الطلبة باساسيات ومختلف التقنيات المتعلقة بالاجهزة والدوائر الالكترونية ضمن منهج متكامل ليتعرف الطالب على الدوائر الالكترونية وطرق تصميمها واستخدامها في تطبيقات عملية عديدة.

# فهرس المحتويات

| الصفحة | الموضوع                                    | م  |  |  |

|--------|--------------------------------------------|----|--|--|

| 2      | المقدمة                                    | 1  |  |  |

| 4      | وصف المقرر                                 |    |  |  |

| 13     | ارشادات الطلبة                             | 3  |  |  |

| 14     | الوحدة الأولى - المحاضرة الأولى            | 4  |  |  |

| 20     | الوحدة الأولى - المحاضرة الثانية           | 5  |  |  |

| 27     | الوحدة الثانية ـ المحاضرة الثالثة          | 6  |  |  |

| 49     | الوحدة الثانية ـ المحاضرة الرابعة          | 7  |  |  |

| 58     | الوحدة الثانية ـ المحاضرة الخامسة          | 8  |  |  |

| 67     | الوحدة الثالثة ـ المحاضرة السادسة          | 9  |  |  |

| 71     | الوحدة الرابعة ـ المحاضرة السابعة          | 10 |  |  |

| 75     | الوحدة الرابعة - المحاضرة الثامنة          | 11 |  |  |

| 79     | الوحدة الرابعة - المحاضرة التاسعة          | 12 |  |  |

| 82     | الوحدة الرابعة ـ المحاضرة العاشرة          | 13 |  |  |

| 86     | الوحدة الرابعة ـ المحاضرة الحادية عشر      | 14 |  |  |

| 89     | الوحدة الرابعة - المحاضرة الثانية عشر      | 15 |  |  |

| 92     | الوحدة الرابعة - المحاضرة الثالثة عشر      | 16 |  |  |

| 95     | الوحدة الرابعة - المحاضرة الرابعة عشر      | 17 |  |  |

| 99     | الوحدة الرابعة - المحاضرة الخامسة عشر      | 18 |  |  |

| 102    | الوحدة الرابعة - المحاضرة السادسة عشر      | 19 |  |  |

| 105    | الوحدة الرابعة - المحاضرة السابعة عشر      |    |  |  |

| 109    | الوحدة الخامسة ـ المحاضرة الثامنة عشر      | 21 |  |  |

| 117    | الوحدة الخامسة ـ المحاضرة التاسعة عشر      | 22 |  |  |

| 121    | الوحدة الخامسة ـ المحاضرة العشرون          | 23 |  |  |

| 127    | الوحدة الخامسة ـ المحاضرة الحادية والعشرون | 24 |  |  |

| 132    | الوحدة الخامسة ـ المحاضرة الثانية والعشرون | 25 |  |  |

| 136    | الوحدة الخامسة ـ المحاضرة الثالثة والعشرون | 26 |  |  |

| 138    | الوحدة السادسة - المحاضرة الرابعة والعشرون | 27 |  |  |

| 142    | الوحدة السادسة – المحاضرة الخامسة والعشرون | 28 |  |  |

| 146    | الوحدة السادسة – المحاضرة السادسة والعشرون | 29 |  |  |

| 150    | الوحدة السادسة - المحاضرة السابعة والعشرون | 30 |  |  |

| 153    | الوحدة السادسة - المحاضرة الثامنة والعشرون | 31 |  |  |

| 157    | الوحدة السادسة - المحاضرة التاسعة والعشرون | 32 |  |  |

| 161    | الوحدة السادسة ـ المحاضرة الثلاثون         | 33 |  |  |

### وصف المقرر الدراسي

يوفر وصف المقرر هذا إيجازاً مقتضياً لأهم خصائص المقرر ومخرجات التعلم المتوقعة من الطالب تحقيقها مبرهناً عما إذا كان قد حقق الاستفادة القصوى من فرص التعلم المتاحة. ولابد من الربط بينها وبين وصف البرنامج. ؟

| كلية الرشيد الجامعة         | 1. المؤسسة التعليمية            |

|-----------------------------|---------------------------------|

| هندسة تقنيات الاجهزة الطبية | 2. القسم العلمي / المركز        |

| مكونات ودوائر الكترونية     | 3. اسم / رمز المقرر             |

| اسبوعيا 2 نظري و 3 عملي     | 4. أشكال الحضور المتاحة         |

| سنوي                        | 5. الفصل / السنة                |

| 150 ساعة                    | 6. عدد الساعات الدراسية (الكلي) |

| 1/9/2022                    | 7. تاريخ إعداد هذا الوصف        |

|                             | 8. أهداف المقرر                 |

- -تعريف الطَّالَب بالدوائر الالكترونية الاساسية وطرق تصميمها واستخدامها وطرق تصميم بعض الدوائر -فهم ومعرفة التطبيقات العملية لديود والانترانسستر. -

- فهم ومعرفة مضخمات الاشارة الكهربائية وانواعها.

- -التطبيقات العملية للمضخمات والدوائر الكهربائية المستخدمة

### 9. مخرجات المقرر وطرائق التعليم والتعلم والتقييم

- أ- الأهداف المعرفية إن يكون الطالب قادر اعلى إن -

- أ 1 التعرف على منحنى خصائص الاشارة الخارجة من الدايود والتطبيقات العملية التي تستخدم بيها. -

- أ 2 استخدام بعض الاجهزة المختبرية والتعرف على تطبيقاتها. -

- أ 3 تصميم بعض الدوائر الالكترونية.

- ب الأهداف المهار آتية الخاصة بالمقرر إن يكون الطالب قادرا على ان: -

- ب 1 حساب القيم الداخلة والخارجة من الدوائر التي تحتوي على الدايود. -

- ب 2 استخدام بعض الاجهزة المختبرية والتعرف على تطبيقاتها -

- ب 3 تصميم بعض الدوائر الالكترونية

- ج- الأهداف الوجدانية و القيمية

- ج1- يلتزم بأخلاقيات المؤسسة التعليمية

- ج2- يعمل بروح الفريق

- ج3- يستقبل ويتقبل المعرفة

#### طرائق التعليم والتعلم

- 1- محاضرات صفية

- 2- وسائل الايضاح (data show)

- 3- ورش عمل

- 4- مختبرات علمبة

- 5- كتب و رقية و الكتر ونية

- طرائق التقييم 1- الامتحانات العملية

- 2- الامتحانات او التغذية الراجعة feed back

- 3- الواجبات البيتية

- 4- الحضور اليومي

- 5- تقار بر مختبرية

- 6- الامتحانات الفصلية النهائية

- د المهار ات العامة و التأهيلية المنقولة (المهار ات الأخرى المتعلقة بقابلية التوظيف و التطور الشخصي).

- د1- مهارة الالقاء وابداء الراي في المحاضرة من خلال seminar

- د2- مهارة المناقشة في المحاضرة د3- مهارة حل المشكلات من خلال ورش العمل

- د4- زيادة قدرة الطالب على استخدام الاجهزة المختبرية.

### 10. بنية المقرر

| طريقة<br>التقييم                | طريقة<br>التعليم                 | المادة النظرية                                                    | الساعات | الاسبوع         |

|---------------------------------|----------------------------------|-------------------------------------------------------------------|---------|-----------------|

| الواجبات البيتية                | محاضرات صفية + data<br>show      | Introduction to semiconductor materials and diode characteristics | 10      | 2-1             |

| الامتحانات<br>+الواجبات البيتية | محاضرات صفية + data<br>show      | DC diode applications                                             | 10      | 4-3             |

| الامتحانات<br>+الواجبات البيتية | محاضرات صفية + data<br>show      | AC diode applications                                             | 10      | 6-5             |

| الامتحانات<br>+الواجبات البيتية | ah ayy lah aya ata gisti a aya d |                                                                   | 5       | 7               |

| الامتحانات<br>+الواجبات البيتية | محاضرات صفية + data<br>show      | BJT transistor characteristics                                    | 15      | 10-9-8          |

| الامتحانات<br>+الواجبات البيتية | محاضرات صفية + data<br>show      | DC analysis of BJT transistor                                     | 15      | -12-11<br>13    |

| الامتحانات<br>+الواجبات البيتية | محاضرات صفية + data<br>show      | AC analysis of BJT transistor                                     | 20      | -15-14<br>17-16 |

| الامتحانات<br>+الواجبات البيتية | محاضرات صفية + data<br>show      | FET transistor<br>characteristics and<br>applications             | 20      | 18-19-<br>20-21 |

| الامتحانات<br>+الواجبات البيتية | محاضرات صفية + data<br>show      | Frequency response                                                | 10      | 23-22           |

| الامتحانات<br>+الواجبات البيتية | محاضرات صفية + data<br>show      | Operational Amplifiers and their applications                     | 20      | -25-24<br>27-26 |

| الامتحانات<br>+الواجبات البيتية | محاضرات صفية + data<br>show      | Power Amplifier                                                   | 15      | -29-28<br>30    |

|                                                              | 10. البنية التحتية                                                |

|--------------------------------------------------------------|-------------------------------------------------------------------|

| Fundamentals of Electronics: Book 1:                         | 1ـ الكتب المقررة المطلوبة                                         |

| Electronic Devices and Circuit Applications                  |                                                                   |

| Morgan & Claypool Publishers                                 |                                                                   |

| Electronic Devices and Circuit Applications                  | 2- المراجع الرئيسية (المصادر)                                     |

| Morgan & Claypool Publishers lectronic                       |                                                                   |

| Devices and Circuit Theory (11th Edition                     |                                                                   |

| Robert L. Boylestad, Louis Nashelsky                         |                                                                   |

| الالي التحكم كتاب والالكترونية الكهربائية الدوائر تحليل كتاب | ا ـ الكتب و المراجع التي يوصى بها                                 |

| وجيه                                                         | ا ـ الكتب والمراجع التي يوصى بها ( المجلات العلمية , التقارير , ) |

| جر جیس                                                       |                                                                   |

| The art of Electronice                                       |                                                                   |

|                                                              | ب ـ المراجع الالكترونية, مواقع الانترنيت                          |

|                                                              |                                                                   |

|                                                              |                                                                   |

|                                                              |                                                                   |

| ر المقرر الدراسي                                                     | خطة تطوير     | .11        |

|----------------------------------------------------------------------|---------------|------------|

|                                                                      | المقرر من خلا | سيتم تطوير |

| ما يستجد من كتب وبحوث تتعلق بدوائر الالكترونية بي المستوعبات العلمية |               |            |

| سكوباس وكلاريفيت                                                     |               |            |

#### HIGHER EDUCATION PERFORMANCE REVIEW: PROGRAMME REVIEW

#### COURSE SPECIFICATION

This Course Specification provides a concise summary of the main features of the course and the learning outcomes that a typical student might reasonably be expected to achieve and demonstrate if he/she takes full advantage of the learning opportunities that are provided. It should be cross-referenced with the programme specification.

| 1. Teaching Institution                                                                                                                | Electrical engineering technical colleges                       |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--|--|--|

| 2. University Department/Centre                                                                                                        | Department of medical instrumentation<br>engineering techniques |  |  |  |

| 3. Course title/code                                                                                                                   | Electronic                                                      |  |  |  |

| Programme(s) to which it contributes                                                                                                   |                                                                 |  |  |  |

| 5. Modes of Attendance offered                                                                                                         | Theory , laboratory                                             |  |  |  |

| 6. Semester/Year                                                                                                                       | YEAR                                                            |  |  |  |

| 7. Number of hours tuition (total)                                                                                                     | 150 hours ( 60 theory + 90 practice)                            |  |  |  |

| Date of production/revision of this specification                                                                                      | 1/9/2022                                                        |  |  |  |

| 9. Aims of the Course                                                                                                                  |                                                                 |  |  |  |

| clarify the properties of electronic materials a     Understand and know the practical application                                     |                                                                 |  |  |  |

| 3. Understand and know the types of transistors and the principle of each one's work                                                   |                                                                 |  |  |  |

| Identify the electric signal amplifiers and their types     Understand the practical applications of amplifiers and electrical circuit |                                                                 |  |  |  |

| Vanishing and production approximated to see a                                                                                         |                                                                 |  |  |  |

|                                                                                                                                        |                                                                 |  |  |  |

|                                                                                                                                        |                                                                 |  |  |  |

#### 10. Learning Outcomes, Teaching ,Learning and Assessment Methode

A- Knowledge and Understanding

Al. Identify the characteristics of the curve of the output signal of the diode and the practical applications in which it is used

A2. Understand the transistor characteristics and identify the input and output

signal of the transistor

A3. Become acquainted with different types of the transistor.

A4. Become familiar with the frequency response of a BJT and FET amplifier.

A5. Understand the different types of operational amplifier, their applications and frequency response of their amplifiers

A6. know the integrated circuits

B. Subject-specific skills

B1. Calculate the input and output values of the electronic circuits that contain the diode or transistor

B2. design circuits according to certain values

**B**3

#### Teaching and Learning Methods

Academic lectures that contribute to establishing a strong foundation to support the cognitive ability of the student

practical laboratory, which provides practical experience to the student through practical experiments, which in turn support and promote the understanding and perception of the theoretical side

#### Assessment methods

Interactive assessment conducted directly between student and teacher is one of the feedback methods that faculty members depends on to evaluate the teaching and learning process

Periodic tests provides information on the extent to which student's follow-up the scientific content and the extent to which the given information can be understood

Quarterly tests and a middle course that held the student's interest and follow-up of the scientific material by its theoretical and skill during the entire semester

Final exams are the final seminar in the assessment of the student and interaction and interest in the scientific material during the whole academic year

C. Thinking Skills

C1. Creating creativity among students and find solutions to different problems

C2. Developing students' ability to work as team members with effective results

C3. Developing students' sense of responsibility and psychological preparation

C4. Develop the studiousness in accomplishing the work to reach satisfactory results

#### Teaching and Learning Methods

Motivate the creative side by posing various problems to students and urging them to find appropriate solutions

Forming work teams to assess the results of their work and change their structure periodically to develop the spirit of cooperation and development and motivate students to make intensive efforts to work different roles

#### Assessment methods

Direct assessment where the assessment is done by the teacher directly and write their observations about it

Practical projects and graduation projects and evaluate the student's ability to creativity, achievement and teamwork and ability to find solutions to various scientific problems

- D. General and Transferable Skills (other skills relevant to employability and personal development)

- D1. Calculate the input and output values of the electronic circuits that contain the diode or transistor

- D2. How to design circuits according to certain values

- D3. Know the analysis of any complex electronic circuit

|                                        | 11. Course Structure                   |           |                                                                            |                                     |                        |                   |

|----------------------------------------|----------------------------------------|-----------|----------------------------------------------------------------------------|-------------------------------------|------------------------|-------------------|

| V                                      | Veek                                   | Hou<br>rs | ILOs                                                                       | Unit/Module<br>or Topic Title       | Teaching<br>Method     | Assessment Method |

| 1**-2                                  | <sub>red</sub>                         | 10        | Introduction to<br>semiconductor<br>materials and diode<br>characteristics | semiconducto<br>r materials         | Lecture +<br>practical | Oral test         |

| 3 <sup>rd</sup> -4                     | pa.                                    | 10        | DC diode applications                                                      | Diode<br>applications               | Lecture +<br>practical | Daily test        |

| 5 <sup>th</sup> -6                     | j <sup>a</sup> h                       | 10        | AC diode applications                                                      | Diode<br>applications               | Lecture +<br>practical | Daily test        |

| 7 <sup>th</sup>                        |                                        | 5         | Zener diode<br>characteristics and<br>applications                         | Zener diode                         | Lecture +<br>practical | Daily test        |

| 84-9                                   | a-10a                                  | 15        | BJT transistor<br>characteristics                                          | BJT transistor                      | Lecture +<br>practical | Daily test        |

| 11 <sup>6</sup> -<br>13 <sup>6</sup>   | -12 <sup>6</sup> -                     | 10        | DC analysis of BJT<br>transistor                                           | DC analysis<br>of BJT<br>transistor | Lecture +<br>practical | Daily test        |

| 14 <sup>6</sup> -                      | 15 <sup>th</sup>                       | 20        | AC analysis of BJT<br>transistor                                           | AC analysis<br>of BJT<br>transistor | Lecture +<br>practical | First term exam   |

| 18 <sup>6</sup> -<br>20 <sup>6</sup> - | 19 <sup>6</sup> -<br>21 <sup>6</sup>   | 20        | FET transistor<br>characteristics and<br>applications                      | FET transistor                      | Lecture +<br>practical | Test              |

| 224-                                   | 23 <sup>th</sup>                       | 10        | Frequency response                                                         | Frequency<br>response               | Lecture +<br>practical | Second term exam  |

| 24°-<br>26°-                           | 25 <sup>th</sup> .<br>28 <sup>th</sup> | 20        | Operational<br>Amplifiers and their<br>applications                        | Operational<br>Amplifiers           | Lecture +<br>practical | Test              |

| 28 <sup>6</sup> -                      | 29ª.                                   | 15        | Power Amplifier                                                            | Power<br>Amplifier                  | Lecture +<br>practical | Final exam        |

| 12. Infrastructure                                                                                   |                                                                                                     |

|------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| Required reading:  · CORE TEXTS  · COURSE MATERIALS  · OTHER                                         | Electronic Devices and Circuit Theory<br>Eleventh Edition<br>Robert L. Boylestad<br>Louis Nashelsky |

| Special requirements (include for<br>example workshops, periodicals,<br>IT software, websites)       |                                                                                                     |

| Community-based facilities<br>(include for example, guest<br>Lectures, internship, field<br>studies) |                                                                                                     |

### إرشادات للطلبة

- الرغبة والحماس للتعليم

- كن مشاركاً في جميع الأنشطة

- احترم أفكار المدرس والزملاء

- أنقد أفكار المدرس والزملاء بأدب إن كانت هناك حاجة.

- احرص على استثمار الوقت

- تقبل الدور الذي يسند إليك في المجموعة

- حفز أفراد مجموعتك في المشاركة في النشاطات

- احرص على بناء علاقات طيبة مع المدرس والزملاء أثناء المحاضرة

- احرص على ما تعلمته في المحاضرة وطبقه في الميدان .

- ركز ذهنك بالتعليم واحرص على التطبيق المباشر

- تغلق الموبايل قبل الشروع بالمحاضرة

### الوحدة الأولى - المحاضرة الأولى - الزمن: 120 دقيقة

#### أهداف المحاضرة الاولى:

### يتوقع في نهاية الجلسة أن يكون الطالب قادراً على:

- 1. فهم ومعرفة المواد أشباه الموصلات

- 2. بعض من خصائص الدايود

#### موضوعات المحاضرة الاولى:

- .1definition of the Semiconductor Diodes

- .2types of Semiconductor Diodes

- .3basic operation and characteristics of a diode in

#### الأساليب والأنشطة والوسائل التعليمية

| الوسائل التدريبية |   | الأساليب والأنشطة التدريبية | ٩ |

|-------------------|---|-----------------------------|---|

| جهاز حاسوب        | • | • نشاط التعارف              |   |

| جهاز عرض          | • | • محاضرة                    | 1 |

| سبورة             | • | مناقشة •                    | 1 |

| اوراق واقلام      | • | • سؤال وجواب                |   |

#### خطة إجراءات تنفيذ المحاضرة الاولى

| الزمن بالدقيقة | الإجراءات                             | المحاضرة | الوحدة |

|----------------|---------------------------------------|----------|--------|

| 120            | الترحيب بالطلبة والتعارف معهم         |          |        |

| دقيقة          | التعريف بالبرنامج وأهدافه وأهميته     |          | 4 6 4. |

|                | والبدء باعطاء المادة العلمية للمحاضرة | الأولى   | الأولى |

|                |                                       |          |        |

|                |                                       |          |        |

#### 1.1 SEMICONDUCTOR MATERIALS: Ge, Si, AND GaAs

The construction of every discrete (individual) solid-state (hard crystal structure) electronic device or integrated circuit begins with a semiconductor material of the highest quality.

Semiconductors are a special class of elements having a conductivity between that of a good conductor and that of an insulator.

In general, semiconductor materials fall into one of two classes: single-crystal and compound.

Single-crystal semiconductors such as germanium (Ge) and silicon (Si) have a repetitive crystal structure, whereas compound semiconductors such as gallium arsenide (GaAs), cadmium sulfide (CdS), gallium nitride (GaN), and gallium arsenide phosphide (GaAsP) are constructed of two or more semiconductor materials of different atomic structures.

#### 1.2 COVALENT BONDINGAND INTRINSIC MATERIALS

The fundamental components of an atom are the electron, proton, and neutron. In the lattice structure, neutrons and protons form the nucleus and electrons appear in fixed orbits around the nucleus. The Bohr model for the three materials is provided in Fig. 1.3.

FIG. 1.3

Atomic structure of (a) silicon; (b) germanium; and (c) gallium and arsenic.

As indicated in Fig. 1.3, silicon has 14 orbiting electrons, germanium has 32 electrons, gallium has 31 electrons, and arsenic has 33 orbiting electrons (the same arsenic that is a very poisonous chemical agent). For germanium and silicon there are four electrons in the outermost shell, which are referred to as valence electrons. Gallium has three valence electrons and arsenic has five valence electrons. Atoms that have four valence electrons are called **tetravalent**, those with three are called **trivalent**

, and those with five are called **pentavalent** . The term valence is used to indicate that the potential (ionization potential) required to remove any one of these electrons from the atomic structure is significantly lower than that required for any other electron in the structure.

This bonding of atoms, strengthened by the sharing of electrons, is called covalent bonding.

FIG. 1.4

Covalent bonding of the silicon atom.

Although the covalent bond will result in a stronger bond between the valence electrons and their parent atom, it is still possible for the valence electrons to absorb sufficient kinetic energy from external natural causes to break the covalent bond and assume the "free" state.

The term *free* is applied to any electron that has separated from the fixed lattice structure and is very sensitive to any applied electric fields such as established by voltage sources or any difference in potential. *The external causes include effects such as light energy in the form of photons and thermal energy (heat) from the surrounding medium*.

The term intrinsic is applied to any semiconductor material that has been carefully Refined to reduce the number of impurities to a very low level—essentially as pure as can be made available through modern technology.

.The free electrons in a material due only to external causes are referred to as *intrinsic* carriers.

Table 1.1 compares the number of intrinsic carriers per cubic centimeter (abbreviated n i) for Ge, Si, and GaAs. It is interesting to note that Ge has the highest number and GaAs the lowest. In fact, Ge has more than twice the number as GaAs.

The number of carriers in the intrinsic form is important, but other characteristics of the material are more significant in determining its use in the field. One such factor is the *relative mobility*  $(m \ n)$  of the free carriers in the material, that is, the ability of the free carriers to move throughout the material.

Table 1.2 clearly reveals that the free carriers in GaAs have more than five times the mobility of free carriers in Si, a factor that results in response times using GaAs electronic devices that can be up to five times those of the same devices made from Si.

Note also that free carriers in Ge have more than twice the mobility of electrons in Si, a factor that results in the continued use of Ge in high-speed radio frequency applications

TABLE 1.1

Intrinsic Carriers n<sub>i</sub>

| Semiconductor | Intrinsic Carriers<br>(per cubic centimeter) |

|---------------|----------------------------------------------|

| GaAs          | $1.7 \times 10^{6}$                          |

| Si            | $1.5 \times 10^{10}$                         |

| Ge            | $2.5 \times 10^{13}$                         |

TABLE 1.2

Relative Mobility Factor  $\mu_n$

| Semiconductor | $\mu_n  (\text{cm}^2/\text{V·s})$ |

|---------------|-----------------------------------|

| Si            | 1500                              |

| Ge            | 3900                              |

| GaAs          | 8500                              |

#### 1.4 ENERGY LEVELS

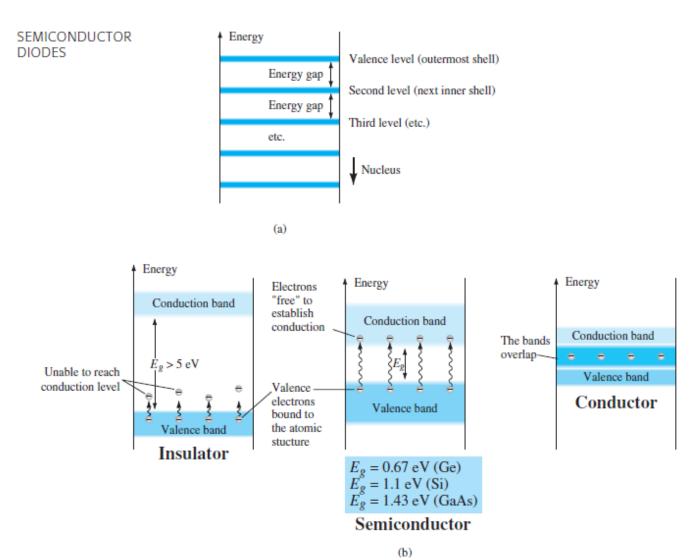

Within the atomic structure of each and every isolated atom there are specific energy levels associated with each shell and orbiting electron, as shown in Fig.1.6.

The energy levels associated with each shell will be different for every element. However, in general:

The farther an electron is from the nucleus, the higher is the energy state, and any electron that has left its parent atom has a higher energy state than any electron in the atomic structure.

Note in Fig. 1.6a that only specific energy levels can exist for the electrons in the atomic structure of an isolated atom. The result is a series of gaps between allowed energy levels

An electron in the valence band of silicon must absorb more energy than one in the valence band of germanium to become a free carrier. Similarly, an electron in the valence band of gallium arsenide must gain more energy than one in silicon or germanium to enter the conduction band.

### الوحدة الأولى - المحاضرة الثانية - الزمن: 120 دقيقة

أهداف المحاضرة الثانية:

### يتوقع في نهاية الجلسة أن يكون الطالب قادراً على:

التعرف على عدد من الدايودات المختلفة ومعرفة الفرق بينها موضوعات المحاضرة الثانية:

n -TYPE AND p -TYPE MATERIALS

SEMICONDUCTOR DIODE

#### الأساليب والأنشطة والوسائل التعليمية

| الوسائل التعليمية | الأساليب والأنشطة التعليمية | م |

|-------------------|-----------------------------|---|

| • جهاز حاسوب      |                             |   |

| • جهاز عرض        | • محاضرة                    | 1 |

| • سبورة           | • مناقشة                    | 1 |

| • اوراق واقلام    | • سؤال وجواب                |   |

المادة العلمية:

1.5 n -TYPE AND p -TYPE MATERIALS

## A semiconductor material that has been subjected to the doping process is called an extrinsic material.

There are two extrinsic materials of immeasureable importance to semiconductor device fabrication: n -type and p -type materials. Each is described in some detail in the following subsections.

#### n -Type Material

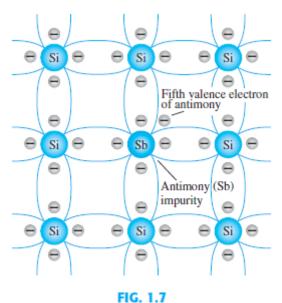

An n -type material is created by introducing impurity elements that have five valence electrons( pentavalent ), such as antimony , arsenic , and phosphorus The effect of such impurity elements is indicated in Fig. 1.7 (using antimony as the impurity in a silicon base). Note that the four covalent bonds are still present. There is, however, an additional fifth electron due to the impurity atom, which is unassociated with any particular covalent bond, This remaining electron, loosely تامه حریه في bound to its parent (antimony) atom,

المنتشره الشوائب Diffused impurities with five valence electrons are called donor المانحة atoms.

Antimony impurity in n-type material.

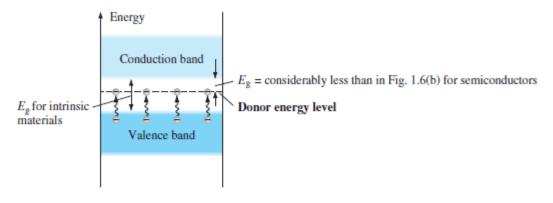

The effect of this doping process on the relative conductivity can best be described through the use of the energy-band diagram of Fig. 1.8. Note that a discrete energy level (called the *donor level*) appears in the forbidden band with an Eg significantly less than that of the intrinsic material.

Those free electrons due to the added impurity sit at this energy level and have less difficulty absorbing a sufficient measure of thermal energy to move into the conduction band at room temperature.

FIG. 1.8

Effect of donor impurities on the energy band structure.

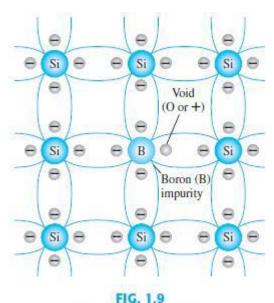

#### p -Type Material

The p -type material is formed by doping a pure germanium or silicon crystal with impurity atoms having three valence electrons. The elements most frequently used for this purpose are boron , gallium , and indium . Each is a member of a subset group of elements in the Periodic Table of Elements referred to as Group III because each has three valence electrons. The effect of one of these elements, boron, on a base of silicon is indicated in Fig. 1.9 .

Note that there is now an insufficient number of electrons to complete the covalent bonds of the newly formed lattice. The resulting vacancy is called a hole and is represented by a small circle or a plus sign, indicating the absence of a negative charge. Since the resulting vacancy will readily accept a free electron:

The diffused impurities with three valence electrons are called acceptor atoms.

The resulting p -type material is electrically neutral, for the same reasons described for the n -type material.

Boron impurity in p-type material.

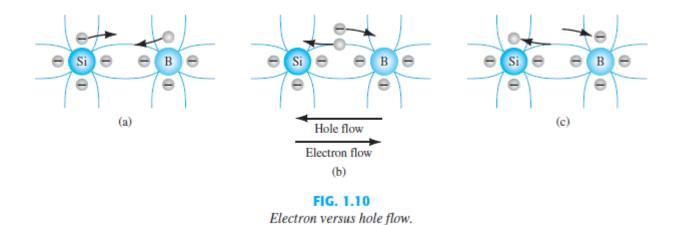

#### **Electron versus Hole Flow**

The effect of the hole on conduction is shown in Fig. 1.10. If a valence electron acquires sufficient kinetic energy to break its covalent bond and fills the void created by a hole, then a vacancy, or hole, will be created in the covalent bond that released the electron. There is, therefore, a transfer of holes to the left and electrons to the right, as shown in Fig. 1.10.

The direction to be used in this text is that of *conventional flow*, which is indicated by the direction of hole flow.

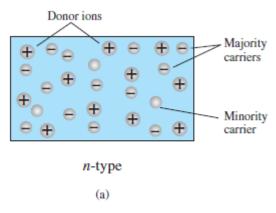

#### **Majority and Minority Carriers**

In an n-type material (Fig. 1.11a) the electron is called the majority carrier and the hole the minority carrier.

In a p-type material the hole is the majority carrier and the electron is the minority carrier. For the p -type material the number of holes far outweighs if the number of electrons,

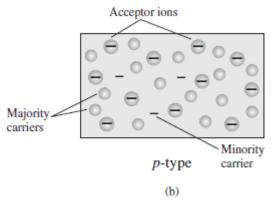

#### 1.6 SEMICONDUCTOR DIODE

Now that both n - and p -type materials are available, we can construct our first solid-state electronic device: The semiconductor diode, is created by simply joining an n -type and a p -type material together

#### No Applied Bias ( $V_0 V$ )

At the instant the two materials are "joined" the electrons and the holes in the region of the junction will combine, resulting in a lack علي of free carriers in the region near the junction, as shown in Fig. 1.12a. Note in Fig. 1.12a that the only particles displayed in this region are the positive and the negative ions remaining once the free carriers have been absorbed.

This region of uncovered positive and negative ions is called the depletion region due to the "depletion" of free carriers in the region.

Under no-bias

conditions, any minority carriers (holes) in the n-type material that find themselves within the depletion region for any reason whatsoever  $\ge 0$  will pass quickly into the p-type material. The closer the minority carrier is to the junction, the greater is the attraction for the layer of negative ions and the less is the opposition offered by the positive ions in the depletion region of the n-type material. We will conclude, therefore, for future discussions, that any minority carriers of the n-type material that find themselves in the depletion region will pass directly into the p-type material. This carrier flow is indicated at the top of Fig. 1.12c for the minority carriers of each material.

In the absence of an applied bias across a semiconductor diode, the net flow of charge in one direction is zero.

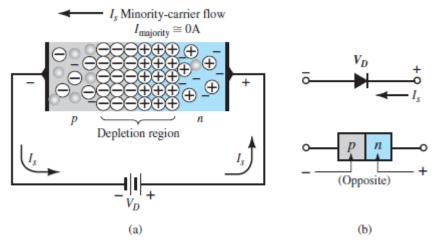

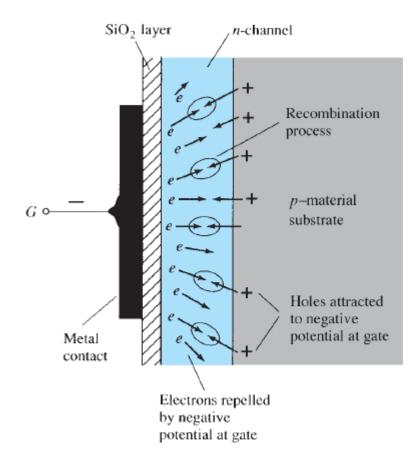

#### Reverse-Bias Condition (VD > 0 V)

If an external potential of V volts is applied across the p-n junction such that the positive terminal is connected to the n-type material and the negative terminal is connected to the p-type material as shown in Fig. 1.13, the number of uncovered positive ions in the depletion region of the n-type material will increase due to the large number of free electrons drawn to the positive potential of the applied voltage. For similar reasons, the number of uncovered negative ions will increase in the p-type material. The net effect, therefore, is a widening of the depletion region. This widening of the depletion region will establish too great a barrier for the majority carriers to overcome, effectively reducing the majority carrier flow to zero, as shown in Fig. 1.13a

The current that exists under reverse-bias conditions is called the reverse saturation current and is represented by Is  $\cdot$

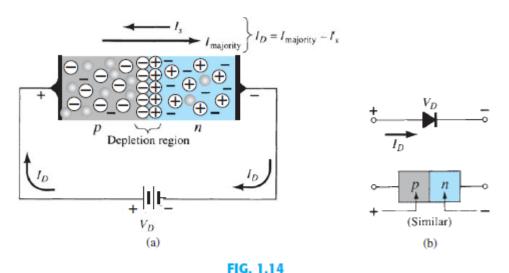

#### Forward-Bias Condition (VD + 0V)

A forward-bias or "on" condition is established by applying the positive potential to the p-type material and the negative potential to the n-type material as shown in Fig. 1.14. The application of a forward-bias potential V D will "pressure" electrons in the n-type material and holes in the p-type material to recombine with the ions near the boundary and reduce the width of the depletion region as shown in Fig. 1.14a. The resulting minority-carrier flow of electrons from the p-type material to the p-type material (and of holes from the p-type material to the p-type material) has not changed in magnitude (since the conduction level is controlled primarily by the limited number of impurities in the material), but the reduction in the width of the depletion region has resulted in a heavy majority flow across the junction

Forward-biased p-n junction: (a) internal distribution of charge under forward-bias conditions; (b) forward-bias polarity and direction of resulting current.

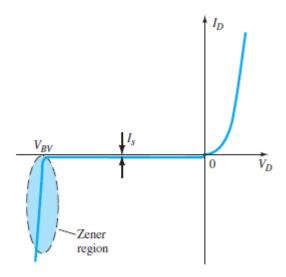

#### **Breakdown Region**

The reverse-bias potential that results in this dramatic change in characteristics is called the breakdown potential and is given the label VBV.

FIG. 1.17

Breakdown region.

The maximum reverse-bias potential that can be applied before entering the breakdown region is called the peak inverse voltage (referred to simply as the PIV rating) or the peak reverse voltage (denoted the PRV rating).

### الوحدة الثانية - المحاضرة الثالثة - الزمن: 120 دقيقة

أهداف المحاضرة

#### يتوقع في نهاية الجلسة أن يكون الطالب قادراً على:

.1Understand the concept of load-line analysis and how it is applied to diode networks.

.2Become familiar with the use of equivalent circuits to analyze series, parallel, and series-parallel diode networks.

3Understand the process of rectification to establish a dc level from a sinusoidal ac input.

موضوعات المحاضرة الثانية:

### DC diode applications

#### الأساليب والأنشطة والوسائل التعليمية

| الوسائل التعليمية       | الأساليب والأنشطة التعليمية | ٩ |

|-------------------------|-----------------------------|---|

| • جهاز حاسوب            | • محاضرة                    |   |

| • جهاز عرض              | • مناقشة                    |   |

| • سبورة<br>اوراق واقلام | سؤال وجواب                  | 1 |

المادة العلمية:

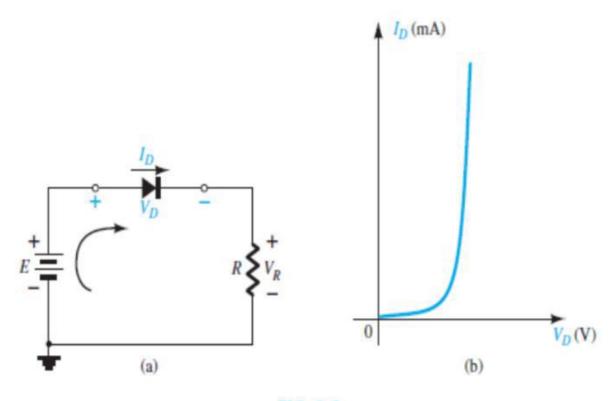

#### **LOAD-LINE ANALYSIS**

The circuit of Fig. 2.1 is the simplest of diode configurations. It will be used to describe the analysis of a diode circuit using its actual characteristics. In the next section we will replace the characteristics by an approximate model for the diode and compare solutions. Solving the circuit of Fig. 2.1 is all about finding the current and voltage levels that will satisfy both the characteristics of the diode and the chosen network parameters at the same time.

FIG. 2.1

Series diode configuration: (a) circuit; (b) characteristics.

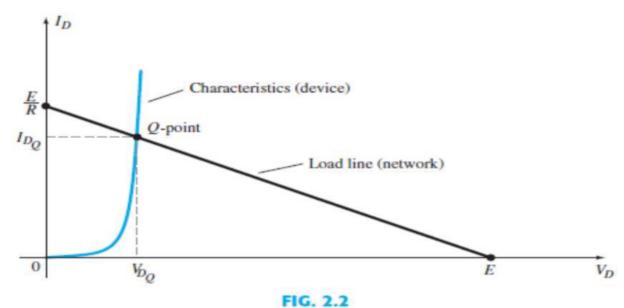

In Fig. 2.2 the diode characteristics are placed on the same set of axes as a straight line defined by the parameters of the network. The straight line is called a load line because the intersection on the vertical axis is defined by the applied load R . The analysis to follow is therefore called load-line analysis. The intersection of the two curves will define the solution for the network and define the current and voltage

$$+E - V_D - V_R = 0$$

$$V_D = E|_{I_D=0 \text{ A}}$$

$$E = V_D + I_D R$$

$$I_D = \frac{E}{R}|_{V_D=0 \text{ V}}$$

#### load line

Drawing the load line and finding the point of operation.

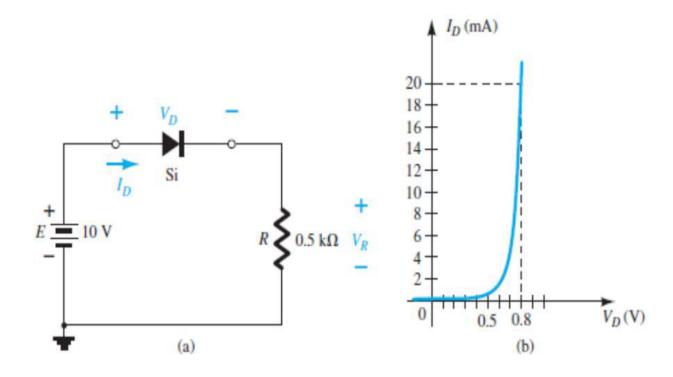

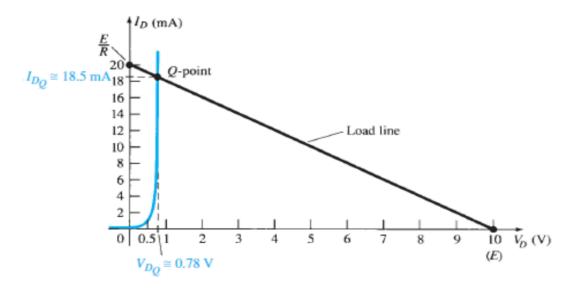

**EXAMPLE** 2.1 For the series diode configuration of Fig. 2.3a, employing the diode characteristics of Fig. 2.3b, determine: a. V<sub>DQ</sub> and I<sub>DQ</sub>. b. V<sub>R</sub>.

FIG. 2.4 Solution to Example 2.1.

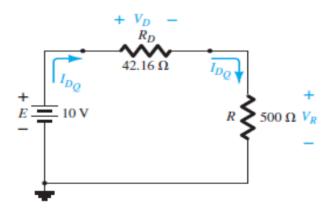

Using the Q-point values, the dc resistance for Example 2.1 is

$$R_D = \frac{V_{D_Q}}{I_{D_O}} = \frac{0.78 \text{ V}}{18.5 \text{ mA}} = 42.16 \Omega$$

An equivalent network (for these operating conditions only) can then be drawn as shown in Fig. 2.5.

FIG. 2.5

Network quivalent to Fig. 2.4.

The current

$$I_D = \frac{E}{R_D + R} = \frac{10 \text{ V}}{42.16 \Omega + 500 \Omega} = \frac{10 \text{ V}}{542.16 \Omega} \cong 18.5 \text{ mA}$$

$$V_R = \frac{RE}{R_D + R} = \frac{(500 \Omega)(10 \text{ V})}{42.16 \Omega + 500 \Omega} = 9.22 \text{ V}$$

and

#### SERIES DIODE CONFIGURATIONS

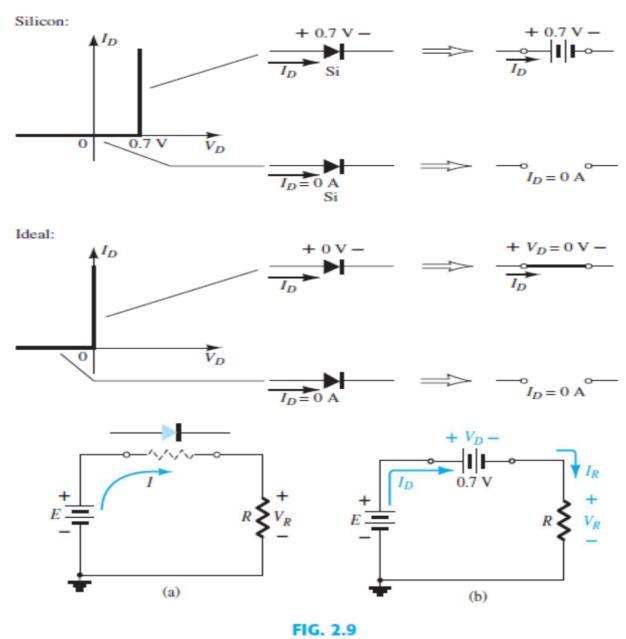

(a) Determining the state of the diode of Fig. 2.8; (b) substituting the equivalent model for the "on" diode of Fig. 2.9a.

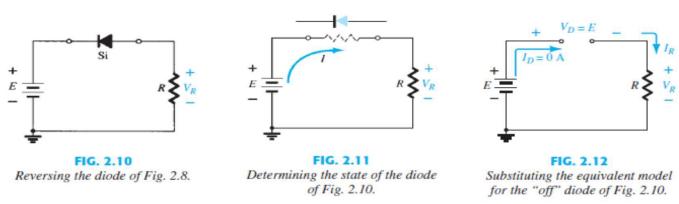

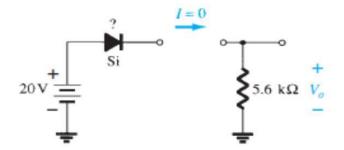

In Fig. 2.10 the diode of Fig. 2.7 has been reversed. Mentally replacing the diode with a resistive element as shown in Fig. 2.11 will reveal that the resulting current direction does not match the arrow in the diode symbol. The diode is in the "off" state, resulting in the equivalent circuit of Fig. 2.12 . Due to the open circuit, the diode current is  $0\,\mathrm{A}$  and the voltage across the resistor R is the following:

# $V_R = I_R R = I_D R = (0 \text{ A}) R = 0 \text{ V}$

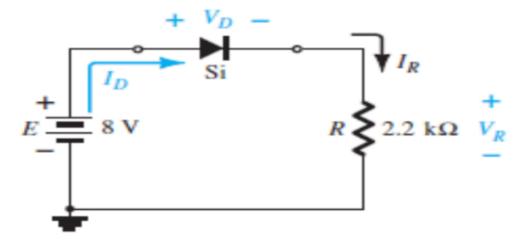

**EXAMPLE 2.4** For the series diode configuration of Fig. 2.13, determine VD, VR, and ID

# FIG. 2.13 Circuit for Example 2.4.

**Solution:** Since the applied voltage establishes a current in the clockwise direction to match the arrow of the symbol and the diode is in the "on" state,

$$V_D = 0.7 \text{ V}$$

$V_R = E - V_D = 8 \text{ V} - 0.7 \text{ V} = 7.3 \text{ V}$

$I_D = I_R = \frac{V_R}{R} = \frac{7.3 \text{ V}}{2.2 \text{ k}\Omega} \approx 3.32 \text{ mA}$

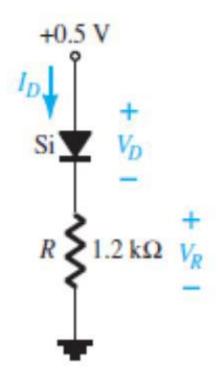

**EXAMPLE 2.6** For the series diode configuration of Fig. 2.16, determine  $V_D$ ,  $V_R$ , and  $I_D$

FIG. 2.16

Series diode circuit for Example 2.6.

**Solution:** Although the "pressure" establishes a current with the same direction as the arrow symbol, the level of applied voltage is insufficient to turn the silicon diode "on." The point of operation on the characteristics is shown in Fig. 2.17, establishing the open-circuit equivalent as the appropriate approximation, as shown in Fig. 2.18. The resulting voltage and current levels are therefore the following:

$$I_D = 0 \text{ A}$$

$V_R = I_R R = I_D R = (0 \text{ A}) 1.2 \text{ k}\Omega = 0 \text{ V}$

$V_D = E = 0.5 \text{ V}$

and

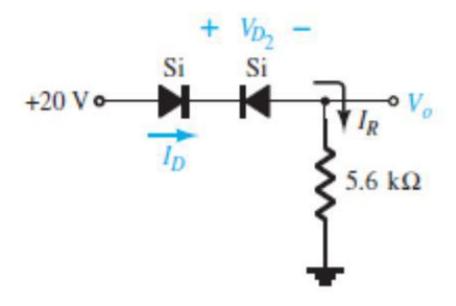

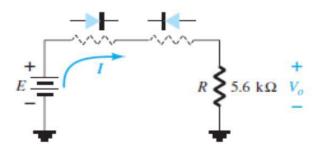

**EXAMPLE 2.8** Determine ID, VD2, and Vo for the circuit of Fig. 2.21 ..

**Solution:** Removing the diodes and determining the direction of the resulting current I result in the circuit of Fig. 2.22. There is a match in current direction for one silicon diode but not for the other silicon diode. The combination of a short circuit in series with an open circuit always results in an open circuit and I D 0 A, as shown in Fig. 2.23.

FIG. 2.18

Determining  $I_D$ ,  $V_R$ , and  $V_D$  for the circuit of Fig. 2.16.

FIG. 2.21

Circuit for Example 2.8.

FIG. 2.22

Determining the state of the diodes of Fig. 2.21.

FIG. 2.23

Substituting the equivalent state for the open diode.

## FIG. 2.24

# Determining the unknown quantities for the circuit of Example 2.8.

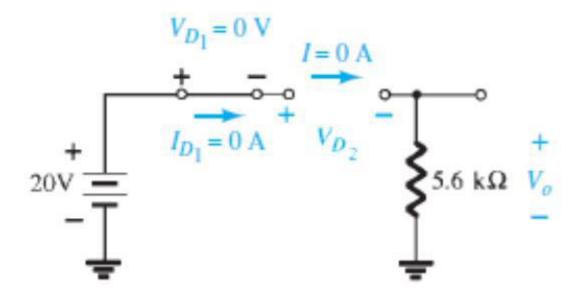

The question remains as to what to substitute for the silicon diode. For the analysis to follow in this and succeeding chapters, simply recall for the actual practical diode that when  $I_D = 0$  A,  $V_D = 0$  V (and vice versa), as described for the no-bias situation in Chapter 1. The conditions described by  $I_D = 0$  A and  $V_{D_1} = 0$  V are indicated in Fig. 2.24. We have

$$V_o = I_R R = I_D R = (0 \text{ A})R = 0 \text{ V}$$

$V_{D_2} = V_{\text{open circuit}} = E = 20 \text{ V}$

Applying Kirchhoff's voltage law in a clockwise direction gives

and

$$E - V_{D_1} - V_{D_2} - V_o = 0$$

$$V_{D_2} = E - V_{D_1} - V_o = 20 \text{ V} - 0 - 0$$

$$= 20 \text{ V}$$

with

$$V_o = 0 \text{ V}$$

#### PARALLEL AND SERIES-PARALLEL CONFIGURATION

The methods applied in Section 2.3 can be extended to the analysis of parallel and series—parallel configurations. For each area of application, simply match the sequential series of steps applied to series diode configurations.

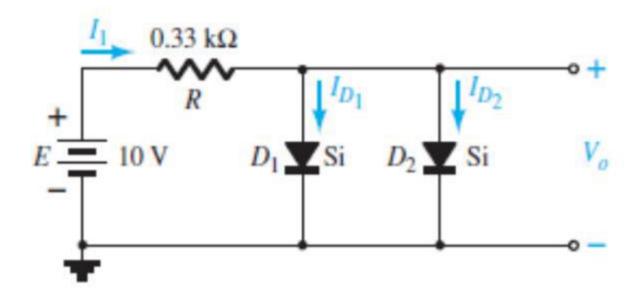

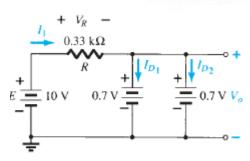

EXAMPLE 2.10 Determine Vo, I1, ID1, and ID2 for the parallel diode configuration of Fig. 2.28

and

FIG. 2.28

Network for Example 2.10.

FIG. 2.29

Determining the unknown quantities for the network of Example 2.10.

Solution: For the applied voltage the "pressure" of the source acts to establish a current through each diode in the same direction as shown in Fig. 2.29. Since the resulting current direction matches that of the arrow in each diode symbol and the applied voltage is greater than 0.7 V, both diodes are in the "on" state. The voltage across parallel elements is always

the same and

$$V_o = 0.7 \, \text{V}$$

The current is

$$I_1 = \frac{V_R}{R} = \frac{E - V_D}{R} = \frac{10 \text{ V} - 0.7 \text{ V}}{0.33 \text{ k}\Omega} = 28.18 \text{ mA}$$

Assuming diodes of similar characteristics, we have

$$I_{D_1} = I_{D_2} = \frac{I_1}{2} = \frac{28.18 \text{ mA}}{2} = 14.09 \text{ mA}$$

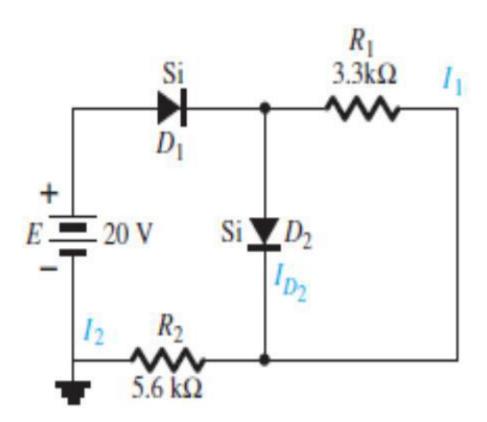

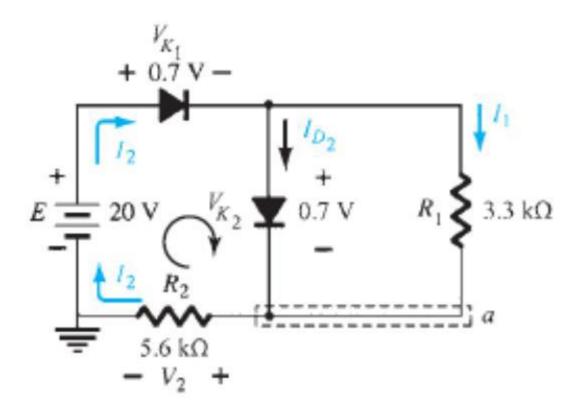

**EXAMPLE 2.13** Determine the currents I1, I2, and ID2 for the network of Fig. 2.37

FIG. 2.37 Network for Example 2.13.

## FIG. 2.38

# Determining the unknown quantities for Example 2.13.

Solution: The applied voltage (pressure) is such as to turn both diodes on, as indicated by the resulting current directions in the network of Fig. 2.38. Note the use of the abbreviated notation for "on" diodes and that the solution is obtained through an application of techniques applied to dc series—parallel networks. We have

$$I_1 = \frac{V_{K_2}}{R_1} = \frac{0.7 \text{ V}}{3.3 \text{ k}\Omega} = 0.212 \text{ mA}$$

Applying Kirchhoff's voltage law around the indicated loop in the clockwise direction yields

$$-V_2 + E - V_{K_1} - V_{K_2} = 0$$

and

$$V_2 = E - V_{K_1} - V_{K_2} = 20 \text{ V} - 0.7 \text{ V} - 0.7 \text{ V} = 18.6 \text{ V}$$

with

$$I_2 = \frac{V_2}{R_2} = \frac{18.6 \text{ V}}{5.6 \text{ k}\Omega} = 3.32 \text{ mA}$$

At the bottom node a,

and

$$I_{D_2} + I_1 = I_2$$

$I_{D_2} = I_2 - I_1 = 3.32 \text{ mA} - 0.212 \text{ mA} \cong 3.11 \text{ mA}$

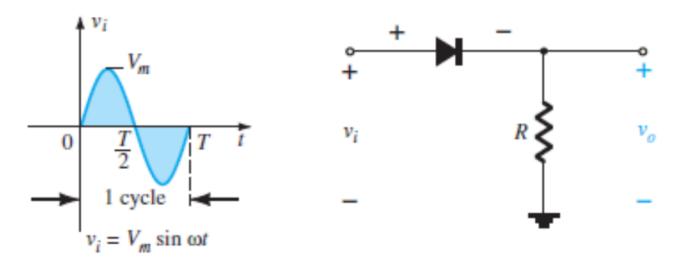

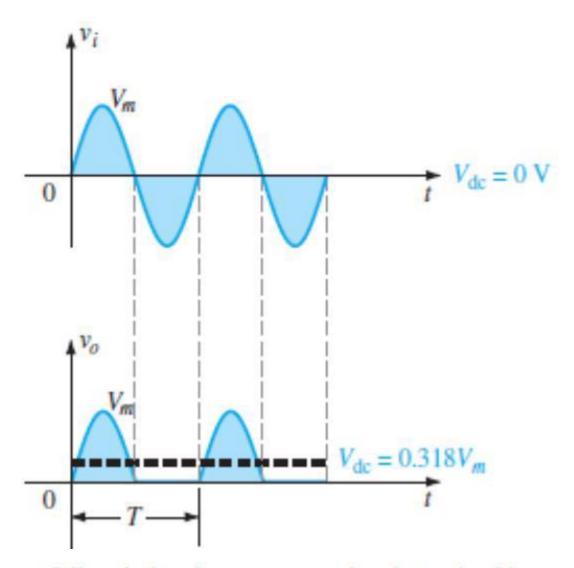

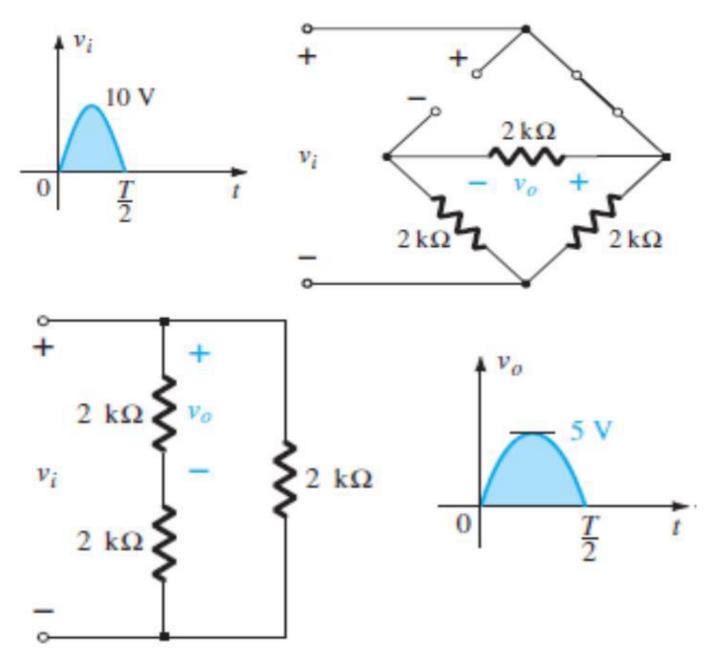

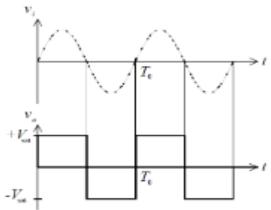

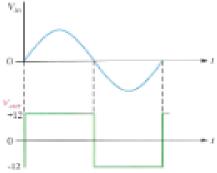

SINUSOIDAL INPUTS; HALF-WAVE RECTIFICATION

The diode analysis will now be expanded to include time-varying functions such as the sinusoidal waveform and the square wave. There is no question that the degree of difficulty will increase, but once a few fundamental maneuvers are understood, the analysis will be fairly direct and follow a common thread.

The simplest of networks to examine with a time-varying signal appears in Fig. 2.44. For the moment we will use the ideal model (note the absence of the Si, Ge, or GaAs label) to ensure that the approach is not clouded by additional mathematical complexity.

FIG. 2.44

Half-wave rectifier.

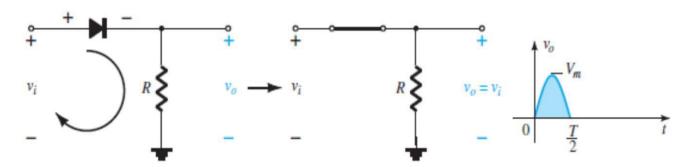

During the interval t=0ST>2 in Fig. 2.44 the polarity of the applied voltage v i is such as to establish "pressure" in the direction indicated and turn on the diode with the polarity appearing above the diode. Substituting the short-circuit equivalence for the ideal diode will result in the equivalent circuit of Fig. 2.45 , where it is fairly obvious that the output signal is an exact replica of the applied signal. The two terminals defining the output voltage are connected directly to the applied signal via the short-circuit equivalence of the diode. For the period T>2ST, the polarity of the input v i is as shown in Fig. 2.46 , and the resulting polarity across the ideal diode produces an "off" state with an open-circuit equivalent. The result is the absence of a path for charge to flow, and v0 = iR = (0)R = 0 V for the period T>2ST. The input v1 is and the output v2 or are sketched together in Fig. 2.47 for comparison purposes. The output signal v3 now has a net positive area above the axis over

FIG. 2.45 Conduction region  $(0 \rightarrow T/2)$ .

FIG. 2.46 Nonconduction region  $(T/2 \rightarrow T)$ .

a full period and an average value determined by

$$V_{\rm dc} = 0.318 \, V_m$$

half-wave

The process of removing one-half the input signal to establish a dc level is called **half wave** rectification

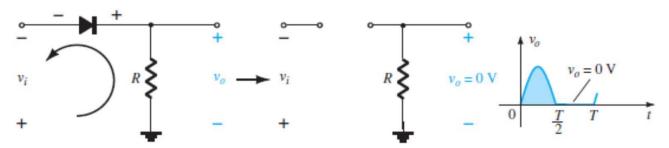

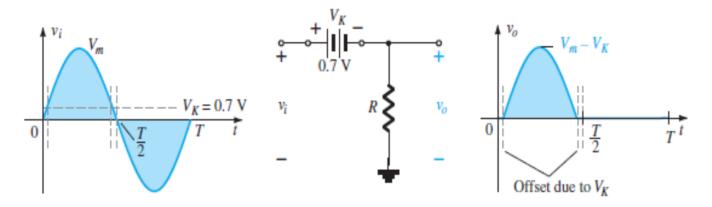

The effect of using a silicon diode with V K 0.7 V is demonstrated in Fig. 2.48 for the forward-bias region. The applied signal must now be at least 0.7 V before the diode can turn "on." For levels of v i less than 0.7 V, the diode is still in an open-circuit state and v o 0 V, as shown in the same figure. When conducting, the difference between v o and v i is a fixed

FIG. 2.48

Effect of  $V_K$  on half-wave rectified signal.

level of V K = 0.7 V and vo = vi - VK, as shown in the figure. The net effect is a reduction in area above the axis, which reduces the resulting dc voltage level. For situations where Vm << VK, the following equation can be applied to determine the average value with a relatively high level of accuracy

$$V_{\rm dc} \simeq 0.318(V_m - V_K)$$

#### **EXAMPLE 2.16**

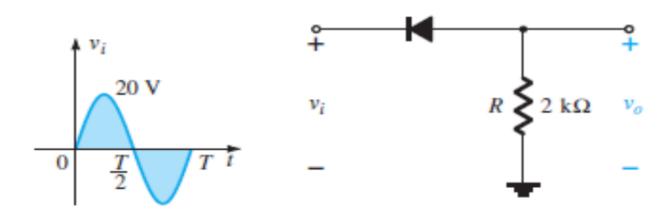

a. Sketch the output v o and determine the dc level of the output for the network of Fig. 2.49

FIG. 2.49 Network for Example 2.16.

### b.

#### Solution:

a. In this situation the diode will conduct during the negative part of the input as shown in Fig. 2.50, and v o will appear as shown in the same figure. For the full period, the dc level is

$$Vdc = -0.318 Vm = -0.318(20 V) = -6.36 V$$

The negative sign indicates that the polarity of the output is opposite to the defined polarity of Fig. 2.49.

FIG. 2.50

Resulting vo for the circuit of Example 2.16.

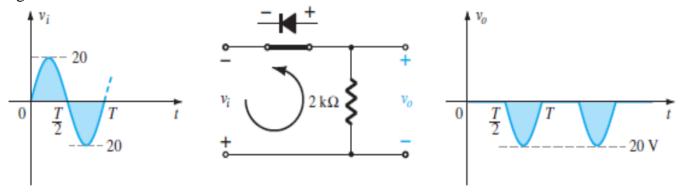

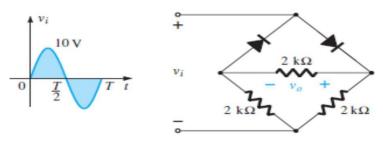

**EXAMPLE 2.17** Determine the output waveform for the network of Fig. 2.64 and calculate the output dc level and the required PIV of each diode.

FIG. 2.64

Bridge network for Example 2.17.

$$V_{\rm dc} = 0.636(5 \text{ V}) = 3.18 \text{ V}$$

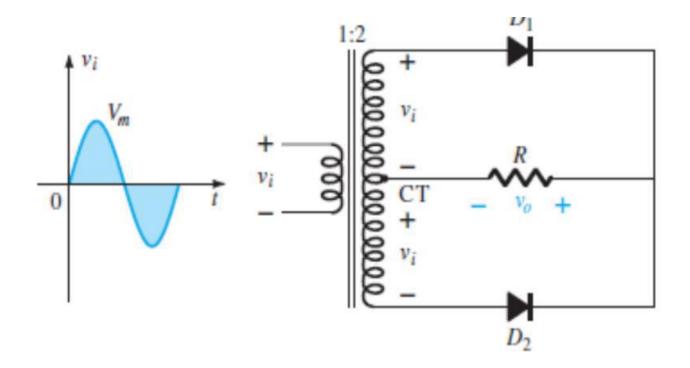

## **Center-Tapped Transformer**

A second popular full-wave rectifier appears in Fig. 2.60 with only two diodes but requiring a center-tapped (CT) transformer to establish the input signal across each section of the secondary of the transformer. During the positive portion of v i applied to the primary of the transformer, the network will appear as shown in Fig. 2.61 with a positive pulse across each section of the secondary coil. D 1 assumes the short-circuit equivalent and D 2 the open-circuit equivalent, as determined by the secondary voltages and the resulting current directions. The output voltage appears as shown in Fig. 2.61

FIG. 2.60

Center-tapped transformer full-wave rectifier.

# الوحدة الثانية - المحاضرة الرابعة - الزمن: 120 دقيقة

## موضوعات المحاضرة الثانية:

### AC diode applications

## الأساليب والأنشطة والوسائل التعليمية

| الوسائل التعليمية                             | الأساليب والأنشطة التعليمية             | ٩ |

|-----------------------------------------------|-----------------------------------------|---|

| <ul><li>جهاز حاسوب</li><li>جهاز عرض</li></ul> | <ul><li>محاضرة</li><li>مناقشة</li></ul> |   |

| • سبورة<br>اوراق واقلام                       | سؤال وجواب<br>اختبار                    | 1 |

## المادة العلمية:

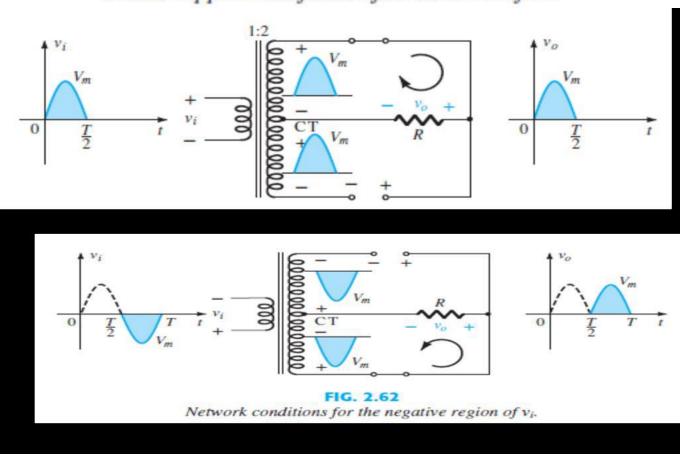

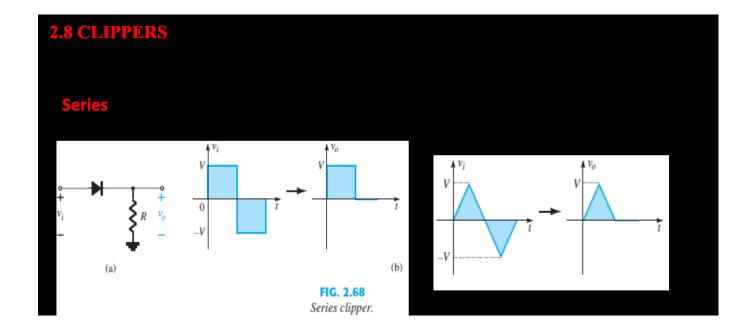

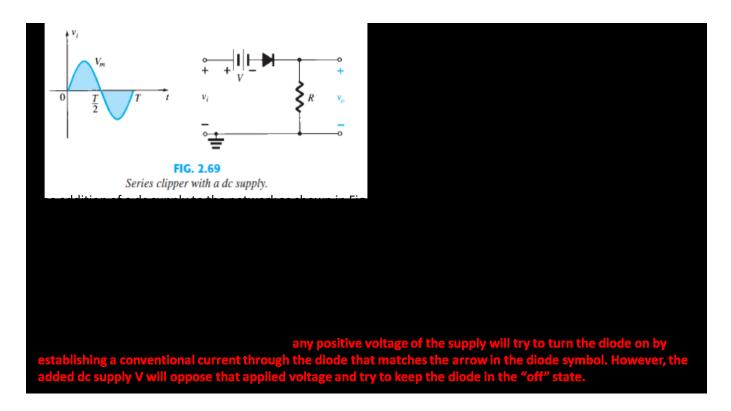

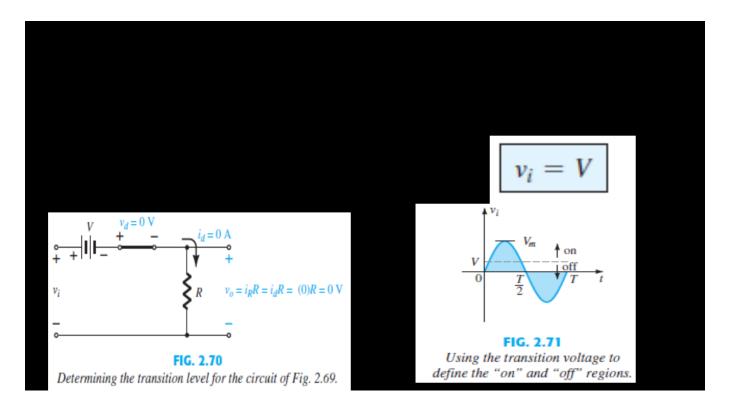

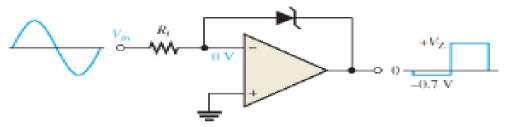

The result is that any supply voltage greater than V volts will turn the diode on and conduction can be established through the load resistor. Keep in mind that we are dealing with an ideal diode for the moment, so the turn-on voltage is simply 0 V. In general, therefore, for the network of Fig. 2.69 we can conclude that the diode will be on for any voltage vi that is greater than Vdc volts and off for any lesser voltage. For the "off" condition, the output would be 0 V due to the lack of current, and for the "on" condition it would simply be vo = vi - V as determined by Kirchhoff's voltage law.

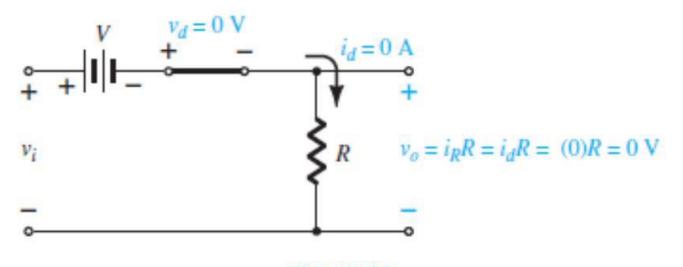

FIG. 2.70

Determining the transition level for the circuit of Fig. 2.69.

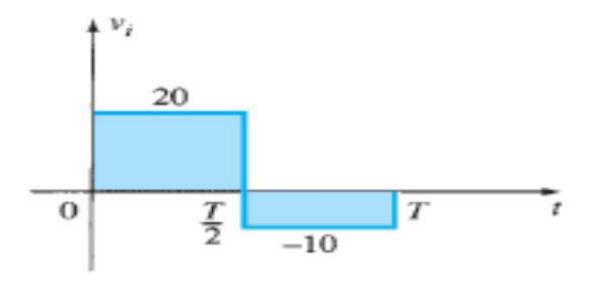

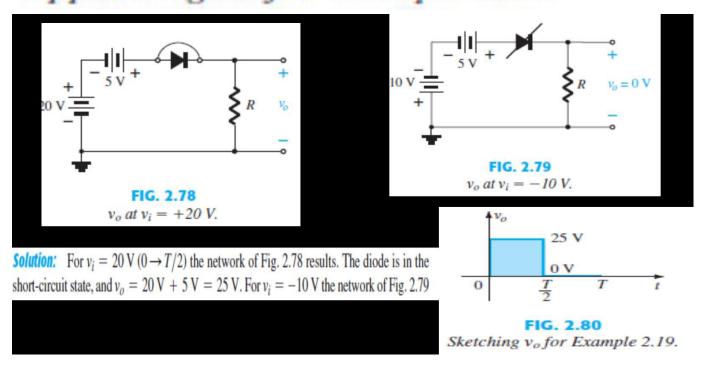

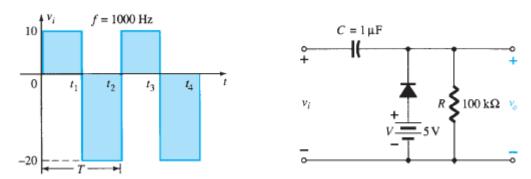

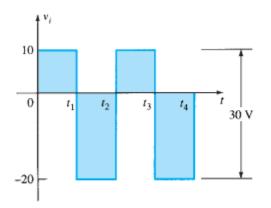

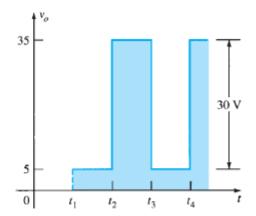

**EXAMPLE 2.19** Find the output voltage for the network examined in Example 2.18 if the applied signal is the square wave of Fig. 2.77.

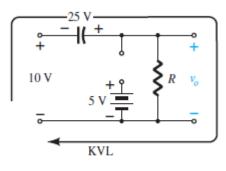

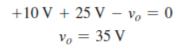

**Solution:** For  $v_i = 20 \text{ V} (0 \rightarrow T/2)$  the network of Fig. 2.78 results. The diode is in the short-circuit state, and  $v_o = 20 \text{ V} + 5 \text{ V} = 25 \text{ V}$ . For  $v_i = -10 \text{ V}$  the network of Fig. 2.79

**Solution**: For vi = 20 V (0 T/2) the network of Fig. 2.78 results. The diode is in the short-circuit state, and vo = 20 V + 5 V = 25 V.

For vi = -10 V the network of Fig. 2.79results, placing the diode in the "off" state, and  $vo = (iR \ R) = (0)R = 0$  V. The resulting output voltage appears in Fig. 2.80

FIG. 2.77

Applied signal for Example 2.19.

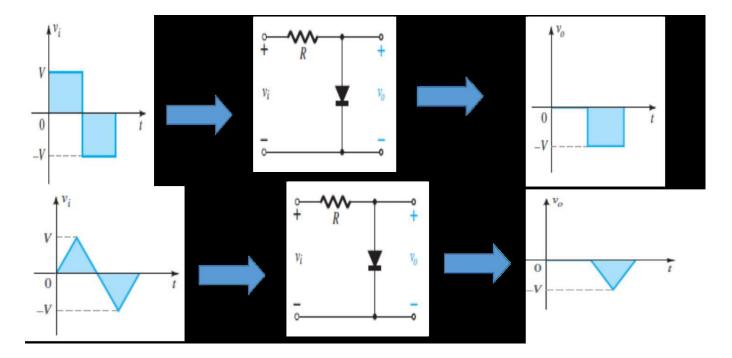

**Parallel**

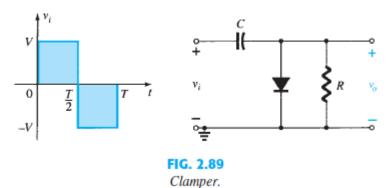

### clamper

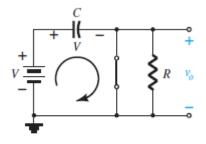

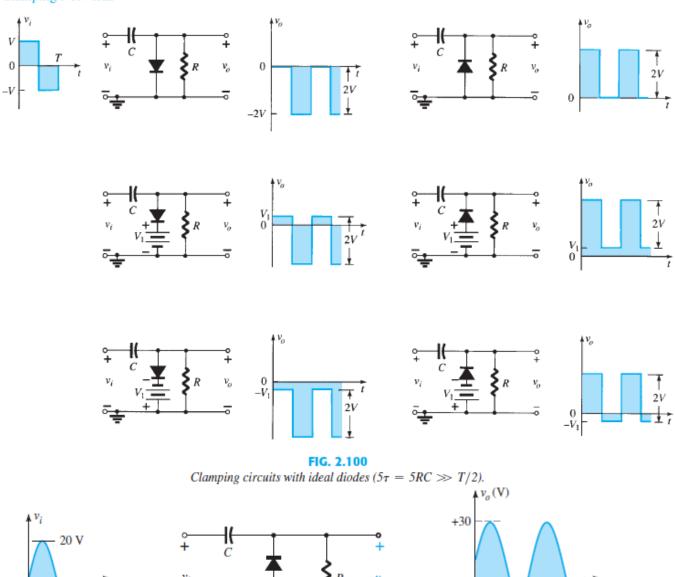

A clamper is a network constructed of a diode, a resistor, and a capacitor that shifts a waveform to a different dc level without changing the appearance of the applied signal. Clamping networks have a capacitor connected directly from input to output with a resistive element in parallel with the output signal. The diode is also in parallel with the output signal but may or may not have a series dc supply as an added element.

There is a sequence of steps that can be applied to help make the analysis straightforward. It is not the only approach to examining clampers, but it does offer an option if difficulties surface.

Step 1: Start the analysis by examining the response of the portion of the input signal that will forward bias the diode

FIG. 2.90

Diode "on" and the capacitor charging to V volts.

Step 2: During the period that the diode is in the "on" state, assume that the capacitor will charge up instantaneously to a voltage level determined by the surrounding network.

Step 3: Assume that during the period when the diode is in the "off" state the capacitor holds on to its established voltage level.

Step 4: Throughout the analysis, maintain a continual awareness of the location and defined polarity for v o to ensure that the proper levels are obtained.

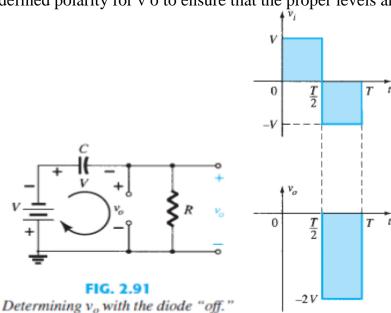

**EXAMPLE 2.22** Determine  $v_o$  for the network of Fig. 2.93 for the input indicated.

FIG. 2.93

Applied signal and network for Example 2.22.

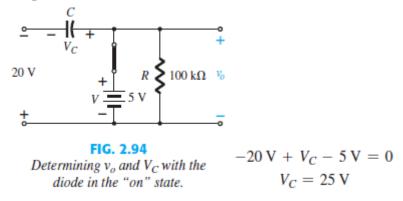

Solution: Note that the frequency is 1000~Hz, resulting in a period of 1 ms and an Interval of 0.5~ms between levels. The analysis will begin with the period t1 St2 of the input signal since the diode is in its short-circuit state. For this interval the network will appear as shown in Fig. 2.94. The output is across R , but it is also directly across the 5-V battery if one follows the direct connection between the defined terminals for vo and the battery terminals. The result is v o =5 V for this interval. Applying Kirchhoff's voltage law around the input loop results in.

The capacitor will therefore charge up to 25 V. In this case the resistor *R* is not shorted

out by the diode, but a Thévenin equivalent circuit of that portion of the network that

includes the battery and the resistor will result in  $RTh = 0 \Omega$  with ETh = V = 5 V. For

the period t2 t3 the network will appear as shown in Fig. 2.95 . The opencircuit equivalent for the diode removes the 5-V battery from having any effect on v o , and applying Kirchhoff's voltage law around the outside loop of the network results in

FIG. 2.95

Determining  $v_o$  with the diode in the "off" state.

FIG. 2.96

$v_i$  and  $v_o$  for the clamper of Fig. 2.93.

#### Clamping Networks

FIG. 2.101

Clamping network with a sinusoidal input.

## الوحدة الثانية - المحاضرة الخامسة - الزمن: 120 دقيقة

أهداف المحاضرة:

يتوقع في نهاية الجلسة أن يكون الطالب قادراً على:

ماهو الزينر دايود وماهى خصائصه

موضوعات المحاضرة الثانية:

### **ZENER DIODES**

### الأساليب والأنشطة والوسائل التعليمية

| الوسائل التعليمية                        | الأساليب والأنشطة التعليمية                 | ٩ |

|------------------------------------------|---------------------------------------------|---|

| • جهاز حاسوب                             | • محاضرة                                    |   |

| <ul><li>جهاز عرض</li><li>سبورة</li></ul> | <ul><li>مناقشة</li><li>سؤال وجواب</li></ul> | 1 |

| اوراق واقلام                             | اختبار                                      |   |

|                                          |                                             |   |

## المادة العلمية:

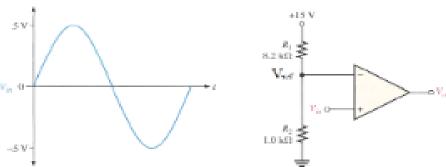

The analysis of networks employing Zener diodes is quite similar to the analysis of semiconductor diodes in previous sections. First the state of the diode must be determined, followed by a substitution of the appropriate model and a determination of the other unknown quantities of the network. **Zener diode can be used to establish reference voltage levels and act as a protection device. voltage reference** is an electronic device which produces a constant voltage regardless of the loading on the device, temperature changes, passage of time and power supply variations. The voltage reference circuit most commonly used in integrated circuits is the bandgap voltage reference

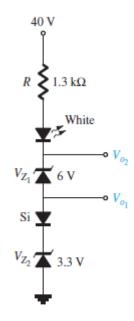

#### **EXAMPLE 2.24**

Determine the reference voltages provided by the network of Fig. 2.109, which uses a white LED to indicate that the power is on. What is the level of current through the LED and the power delivered by the supply? How does the power absorbed by the LED compare to that of the 6-V Zener diode?

Solution: First we have to check that there is sufficient applied voltage to turn on all the series diode elements. The white LED will have a drop of about 4 V across it, the 6-V and 3.3-V Zener diodes have a total of 9.3 V, and the forward-biased silicon diode has 0.7 V, for a total of 14 V. The applied 40 V is then sufficient to turn on all the elements and, one hopes, establish a proper operating current.

FIG. 2.109

Reference setting circuit for

Example 2.24.

Note that the silicon diode was used to create a reference voltage of 4 V because

$$V_{o_1} = V_{Z_2} + V_K = 3.3 \text{ V} + 0.7 \text{ V} = 4.0 \text{ V}$$

Combining the voltage of the 6-V Zener diode with the 4 V results in

$$V_{o_2} = V_{o_1} + V_{Z_1} = 4 \text{ V} + 6 \text{ V} = 10 \text{ V}$$

Finally, the 4 V across the white LED will leave a voltage of 40 V - 14 V = 26 V across the resistor, and

$$I_R = I_{\text{LED}} = \frac{V_R}{R} = \frac{40 \text{ V} - V_{o_2} - V_{\text{LED}}}{1.3 \text{ k}\Omega} = \frac{40 \text{ V} - 10 \text{ V} - 4 \text{ V}}{1.3 \text{ k}\Omega} = \frac{26 \text{ V}}{1.3 \text{ k}\Omega} = 20 \text{ mA}$$

which should establish the proper brightness for the LED.

The power delivered by the supply is simply the product of the supply voltage and current drain as follows:

$$P_s = EI_s = EI_R = (40 \text{ V})(20 \text{ mA}) = 800 \text{ mW}$$

The power absorbed by the LED is

$$P_{\rm LED} = V_{\rm LED} I_{\rm LED} = (4 \text{ V})(20 \text{ mA}) = 80 \text{ mW}$$

and the power absorbed by the 6-V Zener diode is

$$P_Z = V_Z I_Z = (6 \text{ V})(20 \text{ mA}) = 120 \text{ mW}$$

The power absorbed by the Zener diode exceeds that of the LED by 40 mW.

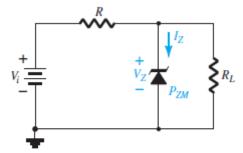

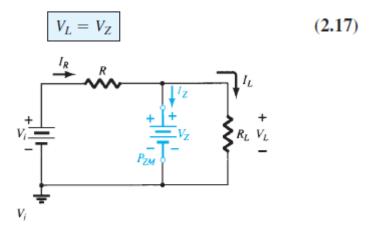

#### Vi and R Fixed

The simplest of Zener diode regulator networks appears in Fig. 2.112. The applied dc voltage

is fixed, as is the load resistor. The analysis can fundamentally be broken down into

two steps.

FIG. 2.112

Basic Zener regulator.

1. Determine the state of the **Zener diode by removing it** from the network and calculating the voltage across the resulting open circuit.

Applying step 1 to the network of Fig. 2.112 results in the network of Fig. 2.113,

wherean application of the voltage divider rule results in

FIG. 2.113

Determining the state of the Zener diode.

$$V = V_L = \frac{R_L V_i}{R + R_L}$$

If  $V \ge V_Z$ , the Zener diode is on, and the appropriate equivalent model can be substituted. If  $V < V_Z$ , the diode is off, and the open-circuit equivalence is substituted.

#### 2. Substitute the appropriate equivalent circuit and solve for the desired unknowns.

For the network of Fig. 2.112, the "on" state will result in the equivalent network of Fig. 2.114. Since voltages across parallel elements must be the same, we find that

FIG. 2.114

Substituting the Zener equivalent for the "on" situation.

The Zener diode current must be determined by an application of Kirchhoff's current law. That is,

$$I_R = I_Z + I_L$$

$$I_Z = I_R - I_L$$

(2.18)

and

where

$$I_L = \frac{V_L}{R_I}$$

and  $I_R = \frac{V_R}{R} = \frac{V_i - V_L}{R}$

The power dissipated by the Zener diode is determined by

$$P_Z = V_Z I_Z \tag{2.19}$$

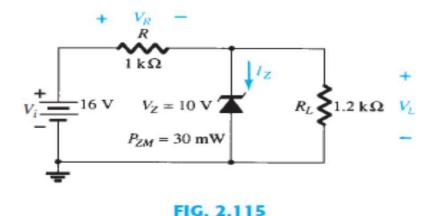

#### **EXAMPLE 2.26**

- a. For the Zener diode network of Fig. 2.115, determine  $V_L$ ,  $V_R$ ,  $I_Z$ , and  $P_Z$ .

- b. Repeat part (a) with  $R_L = 3 \text{ k}\Omega$ .

FIG. 2.115

Zener diode regulator for Example 2.26.

### Solution:

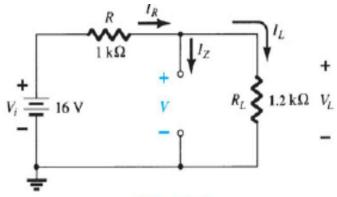

Following the suggested procedure, we redraw the network as shown in Fig. 2.116.

Applying Eq. (2.16) gives

$$V = \frac{R_L V_i}{R + R_L} = \frac{1.2 \text{ k}\Omega (16 \text{ V})}{1 \text{ k}\Omega + 1.2 \text{ k}\Omega} = 8.73 \text{ V}$$

FIG. 2.116

Determining V for the regulator of Fig. 2.115.

Since V = 8.73 V is less than  $V_Z = 10$  V, the diode is in the "off" state, as shown on the characteristics of Fig. 2.117. Substituting the open-circuit equivalent results in the same network as in Fig. 2.116, where we find that

$$V_L = V = 8.73 \text{ V}$$

$V_R = V_i - V_L = 16 \text{ V} - 8.73 \text{ V} = 7.27 \text{ V}$

$I_Z = 0 \text{ A}$

$P_Z = V_Z I_Z = V_Z (0 \text{ A}) = 0 \text{ W}$

and

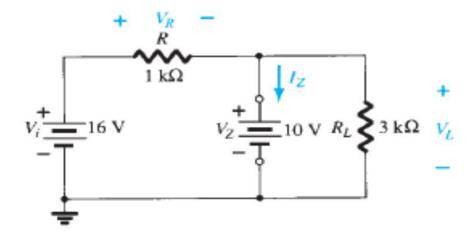

b. Applying Eq. (2.16) results in

$$V = \frac{R_L V_i}{R + R_L} = \frac{3 \text{ k}\Omega(16 \text{ V})}{1 \text{ k}\Omega + 3 \text{ k}\Omega} = 12 \text{ V}$$

Since V = 12 V is greater than  $V_Z = 10$  V, the diode is in the "on" state and the work of Fig. 2.118 results. Applying Eq. (2.17) yields

and

$$V_L = V_Z = 10 \text{ V}$$

$V_R = V_i - V_L = 16 \text{ V} - 10 \text{ V} = 6 \text{ V}$

with  $I_L = \frac{V_L}{R_L} = \frac{10 \text{ V}}{3 \text{ k}\Omega} = 3.33 \text{ mA}$

and  $I_R = \frac{V_R}{R} = \frac{6 \text{ V}}{1 \text{ k}\Omega} = 6 \text{ mA}$

so that  $I_Z = I_R - I_L [\text{Eq. (2.18)}]$

$I_Z = 6 \text{ mA} - 3.33 \text{ mA}$

$I_Z = 2.67 \text{ mA}$

FIG. 2.118

Network of Fig. 2.115 in the "on" state.

The power dissipated is

$$P_Z = V_Z I_Z = (10 \text{ V})(2.67 \text{ mA}) = 26.7 \text{ mW}$$

which is less than the specified  $P_{ZM} = 30 \text{ mW}$ .

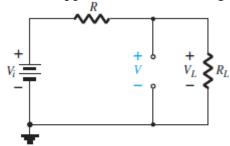

#### Fixed Vi, Variable RL

Due to the offset voltage VZ, there is a specific range of resistor values (and therefore load current) that will ensure that the Zener is in the "on" state. Too small a load resistance RL will result in a voltage VL across the load resistor less than VZ, and the Zener device will be in the "off" state.

To determine the minimum load resistance of Fig. 2.112 that will turn the Zener diode on, simply calculate the value of  $R_L$  that will result in a load voltage  $V_L = V_Z$ . That is,

$$V_L = V_Z = \frac{R_L V_i}{R_L + R}$$

Solving for  $R_L$ , we have

$$R_{L_{\min}} = \frac{RV_Z}{V_i - V_Z} \tag{2.20}$$

Any load resistance value greater than the  $R_L$  obtained from Eq. (2.20) will ensure that the Zener diode is in the "on" state and the diode can be replaced by its  $V_Z$  source equivalent.

The condition defined by Eq. (2.20) establishes the minimum  $R_L$ , but in turn specifies the maximum  $I_L$  as

$$I_{L_{\text{max}}} = \frac{V_L}{R_L} = \frac{V_Z}{R_{L_{\text{min}}}}$$

(2.21)

Once the diode is in the "on" state, the voltage across R remains fixed at

$$V_R = V_i - V_Z \tag{2.22}$$

and  $I_R$  remains fixed at

$$I_R = \frac{V_R}{R} \tag{2.23}$$

The Zener current

$$I_Z = I_R - I_L \tag{2.24}$$

resulting in a minimum  $I_Z$  when  $I_L$  is a maximum and a maximum  $I_Z$  when  $I_L$  is a minimum value, since  $I_R$  is constant.

Since  $I_Z$  is limited to  $I_{ZM}$  as provided on the data sheet, it does affect the range of  $R_L$  and therefore  $I_L$ . Substituting  $I_{ZM}$  for  $I_Z$  establishes the minimum  $I_L$  as

$$I_{L_{\min}} = I_R - I_{ZM} \tag{2.25}$$

and the maximum load resistance as

$$R_{L_{\text{max}}} = \frac{V_Z}{I_{L_{\text{min}}}} \tag{2.26}$$

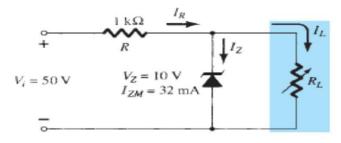

#### **EXAMPLE 2.27**

- a. For the network of Fig. 2.119, determine the range of R<sub>L</sub> and I<sub>L</sub> that will result in V<sub>RL</sub> being maintained at 10 V.

- Determine the maximum wattage rating of the diode.

FIG. 2.119

Voltage regulator for Example 2.27.

#### Solution:

a. To determine the value of  $R_L$  that will turn the Zener diode on, apply Eq. (2.20):

$$R_{L_{\min}} = \frac{RV_Z}{V_i - V_Z} = \frac{(1 \text{ k}\Omega)(10 \text{ V})}{50 \text{ V} - 10 \text{ V}} = \frac{10 \text{ k}\Omega}{40} = 250 \text{ }\Omega$$

The voltage across the resistor R is then determined by Eq. (2.22):

$$V_R = V_i - V_Z = 50 \text{ V} - 10 \text{ V} = 40 \text{ V}$$

and Eq. (2.23) provides the magnitude of  $I_R$ :

$$I_R = \frac{V_R}{R} = \frac{40 \text{ V}}{1 \text{ k}\Omega} = 40 \text{ mA}$$

The minimum level of  $I_L$  is then determined by Eq. (2.25):

$$I_{L_{\min}} = I_R - I_{ZM} = 40 \text{ mA} - 32 \text{ mA} = 8 \text{ mA}$$

with Eq. (2.26) determining the maximum value of  $R_L$ :

$$R_{L_{\text{max}}} = \frac{V_{\text{Z}}}{I_{L_{\text{min}}}} = \frac{10 \text{ V}}{8 \text{ mA}} = 1.25 \text{ k}\Omega$$

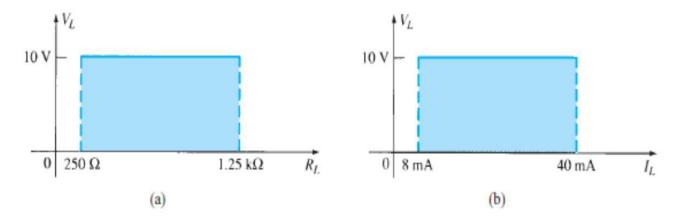

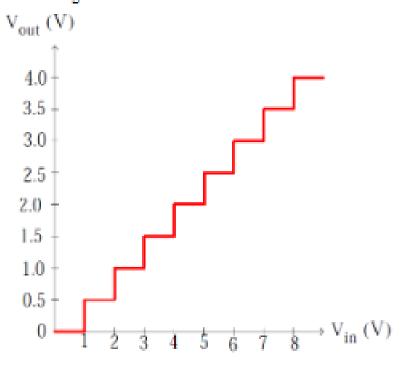

A plot of  $V_L$  versus  $R_L$  appears in Fig. 2.120a and for  $V_L$  versus  $I_L$  in Fig. 2.120b.

FIG. 2.120

$V_L$  versus  $R_L$  and  $I_L$  for the regulator of Fig. 2.119.

b.

$$P_{\text{max}} = V_Z I_{ZM}$$

=  $(10 \text{ V})(32 \text{ mA}) = 320 \text{ mW}$

## الوحدة الثالثة - المحاضرة السادسة - الزمن: 120 دقيقة

#### أهداف المحاضرة:

## يتوقع في نهاية الجلسة أن يكون الطالب قادراً على:

- 1. Become familiar with the basic construction and operation of the Bipolar Junction Transistor.

- 2. Be able to apply the proper biasing to insure operation in the active region.

- 3. Recognize and be able to explain the characteristics of an npn or pnp transistor.

### موضوعات المحاضرة الثانية:

- 1. definition of the Bipolar Junction Transistor.

- 2. Understand the characteristics of an npn or pnp transistor.

- .3. apply the proper biasing to insure operation in the active region الأساليب والانشطة والوسائل التعليمية

| الوسائل التعليمية                                                                     | الأساليب والأنشطة التعليمية                                                    | ٩ |

|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|---|

| <ul> <li>جهاز حاسوب</li> <li>جهاز عرض</li> <li>سبورة</li> <li>اوراق واقلام</li> </ul> | <ul> <li>محاضرة</li> <li>مناقشة</li> <li>سؤال وجواب</li> <li>اختبار</li> </ul> | 1 |

المادة العلمية:

#### 3.1 INTRODUCTION

During the period 1904 to 1947, the vacuum tube was the electronic device of interest and development. In 1904, the vacuum-tube diode was introduced by J. A. Fleming. Shortly thereafter, in 1906, Lee De Forest added a third

element, called the control grid, to the vacuum diode, resulting in the first amplifier, the triode. In the following years, radio and television provided great stimulation to the tube industry. Production rose from about 1 million tubes in 1922 to about 100 million in 1937. In the early 1930s the four element tetrode and the five-element pentode gained prominence in the electron-tube industry. In the years to follow, the industry became one of primary importance, and rapid advances were made in design, manufacturing techniques, high-power and high-frequency applications, and miniaturization. On December 23, 1947, however, the electronics industry was to experience the advent of a completely new direction of interest and development. It was on the afternoon of this day that Dr. S. William Shockley, Walter H. Brattain, and John Bardeen demonstrated the amplifying action of the first transistor at the Bell Telephone Laboratories as shown in Fig. 3.1 . The original transistor (a point-contact transistor) is shown in Fig. 3.2 . The advantages of this three-terminal solid-state device over the tube were immediately obvious:

It was smaller and lightweight; it had no heater requirement or heater loss; it had a rugged construction; it was more efficient since less power was absorbed by the device itself; it was instantly available for use, requiring no warm-up period; and lower operating voltages were possible. Note that this chapter is our first discussion of devices with three or more terminals. You will find that all amplifiers (devices that increase the voltage, current, or power level) have at least three terminals, with one controlling the flow or potential between the other two.

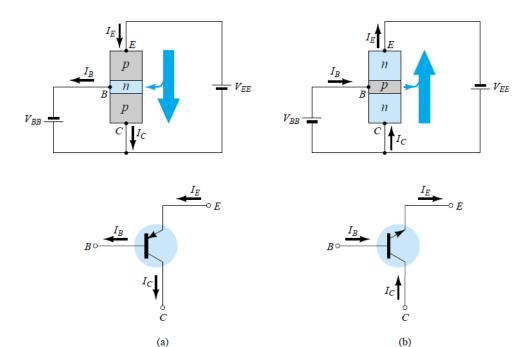

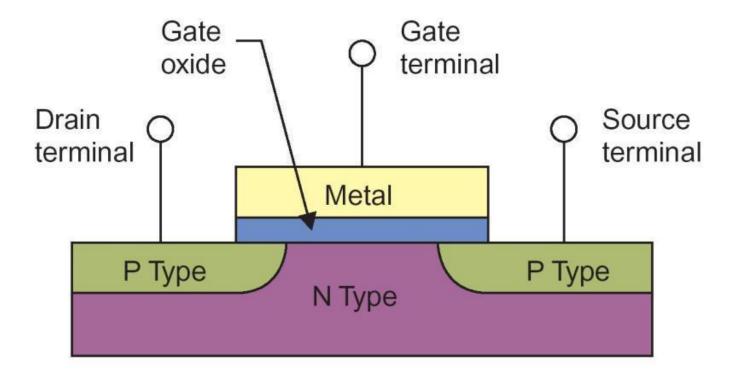

### 3.2-Transistor construction

The transistor is a three-layer semiconductor device consisting of either two n- and one p-type layers of material or two p- and one n-type layers of material. The former is called an NPN transistor, while the latter is called a PnP transistor. Transistor composed from

- 3.2.1-The emitter layer is heavily doped

- 3.2.2- The base lightly doped

- 3.2.3-The collector only lightly doped

This lower doping level decreases the conductivity (increases the resistance) of this material by limiting the number of "free" carriers

The outer layers have widths much greater than the sandwiched p - or n -type material

The terminals have been indicated by the capital letters  $\mathbf{E}$  for emitter,  $\mathbf{C}$  for collector, and  $\mathbf{B}$  for base, the term bipolar reflects the fact that holes and electrons participate in the

injection process into the oppositely polarized material. If only one carrier is employed (electron or hole), it is considered a unipolar device.

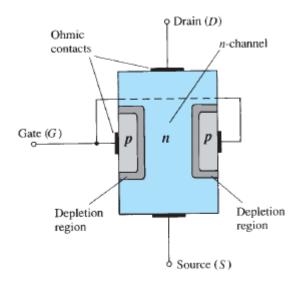

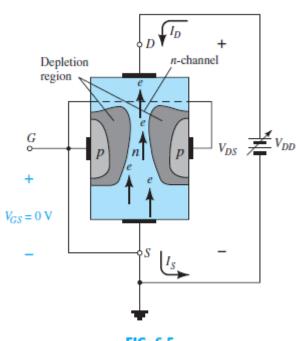

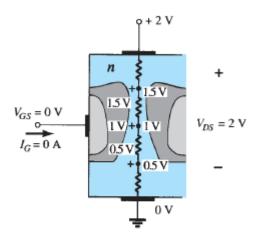

### 3.3 TRANSISTOR OPERATION

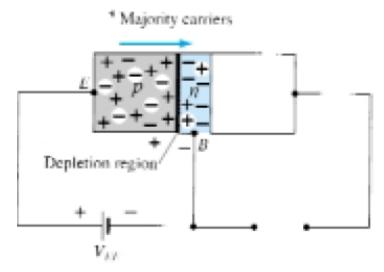

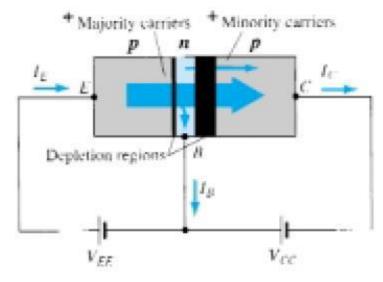

The basic operation of the transistor will now be described using the pnp transistor of Fig. 3.2a. The operation of the npn transistor is exactly the same if the roles played by the electron and hole are interchanged. In Fig. 3.3 the pnp transistor has been redrawn without the base-to-collector bias. The depletion region has been reduced in width due to the applied bias, resulting in a heavy flow of majority carriers from the p- to the n-type material.

**Figure 3.3** Forward-biased junction of a *pnp* transistor.

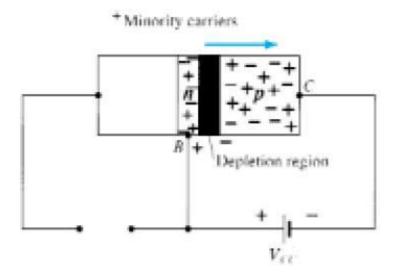

Let us now remove the base-to-emitter bias of the pnp transistor of Fig. 3.2a as shown in Fig. 3.4.. Recall that the flow of majority carriers is zero, resulting in only a minority-carrier flow, as indicated in Fig. 3.4. In summary, therefore:

One p-n junction of a transistor is reverse biased, while the other is forward biased.

**Figure 3.4** Reverse-biased junction of a *pnp* transistor.

In Fig. 3.5 both biasing potentials have been applied to a pnp transistor, with the resulting majority- and minority-carrier flow indicated. Note in Fig. 3.5 the widths of the depletion regions, indicating clearly which junction is forward-biased and which is reverse-biased. As indicated in Fig. 3.5, a large number of majority carriers will diffuse across the forward-biased p-n junction into the n-type material. The question then is whether these carriers will contribute directly to the base current IB or pass directly into the p-type material. Since the sandwiched n-type material is very thin and has a low conductivity, a very small number of these carriers will take this path of high resistance to the base terminal. The magnitude of the base current is typically on the order of microamperes as compared to mill amperes for the emitter and collector currents.

**Figure 3.5** Majority and minority carrier flow of a *pnp* transistor.

Applying Kirchhoff's current law to the transistor of Fig. 3.5 as if it were a single node, we obtain

$$I_E = I_C + I_B \tag{3.1}$$

The majority and minority carriers as indicated in Fig. 3.5. The minority-current component is called the leakage current and is given the symbol **ICO** (**IC** current with emitter terminal Open). The collector current, therefore, is determined in total by Eq. (3.2).

$$I_C = I_{C_{\text{majority}}} + I_{CO_{\text{minority}}} \tag{3.2}$$

For general-purpose transistors, **IC** is measured in milliamperes, while **ICO** is measured in microamperes or nanoamperes. **ICO**, like is for a reverse-biased diode, is temperature sensitive and must be examined carefully when applications of wide temperature ranges are considered. It can severely affect the stability of a system at high temperature if not considered properly. Improvements in construction techniques have resulted in significantly lower levels of **ICO**, to the point where its effect can often be ignored.

- 1- Emitter-Base forward bias junction

- 2- Collector-base- reverse bias junction

## الوحدة الرابعة - المحاضرة السابعة - الزمن: 120 دقيقة

أهداف المحاضرة:

يتوقع في نهاية الجلسة أن يكون الطالب قادراً على: التعرف على مزايا BJT transistor characteristics

موضوعات المحاضرة الثانية:

BJT transistor characteristics

الأساليب والأنشطة والوسائل التعليمية

| الوسائل التعليمية | الأساليب والأنشطة التعليمية | م |

|-------------------|-----------------------------|---|

| • جهاز حاسوب      | • محاضرة                    |   |

| • جهاز عرض        | • مناقشة                    | 1 |

| • سبورة           | سؤال وجواب                  | 1 |

| اوراق واقلام      | اختبار                      |   |

| <u> </u> |  |

|----------|--|

|          |  |

|          |  |

|          |  |

|          |  |

|          |  |

|          |  |

## المادة العلمية:

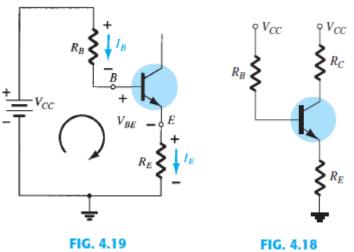

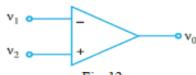

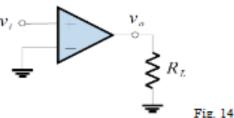

## المشترك الجامع ترانزستور ( COMMON-COLLECTOR CONFIGURATIO )

The third and final transistor configuration is the common-collector configuration, shown in Fig. 3.20 with the proper current directions and voltage notation. The common-collector (purposes since it has توفيق الممانعة configuration is used primarily for impedance-matching) a high input impedance and low output impedance, opposite to that of the common-base and common-emitter configurations.

Figure 3.20 Notation and symbols used with the common-collector configuration: (a) pnp transistor; (b) npn transistor.

3.7 Common-Collector Configuration

A common-collector circuit configuration is provided in Fig. 3.21 with the load resistor connected from emitter to ground. Note that the collector is tied to ground even though the transistor is connected in a manner similar to the common-emitter configuration. From a design viewpoint, there is no need 85

for a set of common collector characteristics to choose the parameters of the circuit of Fig.3.2 It can be designed using the common-emitter characteristics of Section 3.6

127

Figure 3.21 Common-collector configuration used for impedance-matching purposes.

For all practical purposes, the output characteristics of the common-collector configuration are the same as for the common-emitter configuration. For the common-collector configuration the output characteristics are a plot of IE versus VEC for a range of values of IB.

.The input current, therefore, is the same for both the common-emitter and common collector characteristics. The horizontal voltage axis for the common-collector configuration is obtained by simply changing the sign of the collector-to-emitter voltage of the common-emitter characteristics. Finally, there is an almost unnoticeable change in the vertical scale of IC of the common-emitter characteristics if IC is replaced by IE for the common-collector characteristics For the input circuit of the common-collector configuration the common-emitter base characteristics are sufficient for obtaining the required information

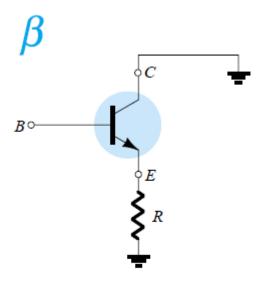

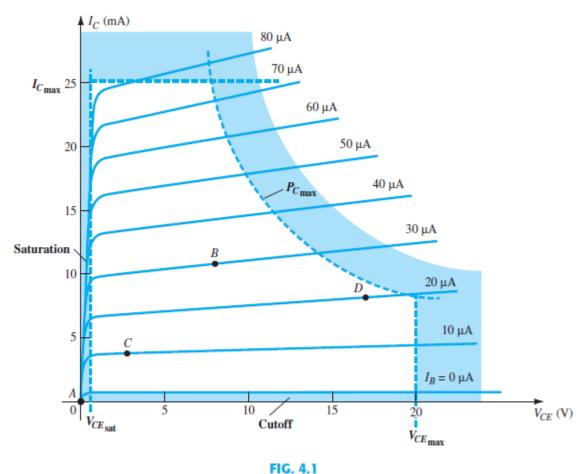

#### 3.9 LIMITS OF OPERATION

For each transistor there is a region of operation on the characteristics which will ensure ) ينجاوز (that the maximum ratings are not being exceeded) ينجاوز

( . Such a region has been اقل تشويه and the output signal exhibits minimum distortion) defined for the transistor characteristics of Fig. 3.22. All of the limits of operation are defined on a typical transistor specification sheet described in Section 3.9.

Some of the limits of operation are self-explanatory, such as maximum collector current (normally referred to on the specification sheet as

continuous collector current) and maximum collector-to-emitter voltage (often abbreviated as VCEO or V(BR)CEO on the specification sheet). For the transistor of Fig. 3.22, ICmax was specified as 50 mA and VCEO as 20 V. The vertical line on the characteristics defined as VCEsat specifies

# الوحدة الرابعة - المحاضرة الثامنة - الزمن: 120 دقيقة

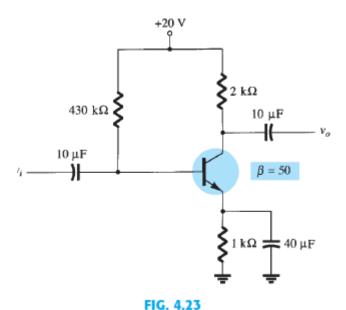

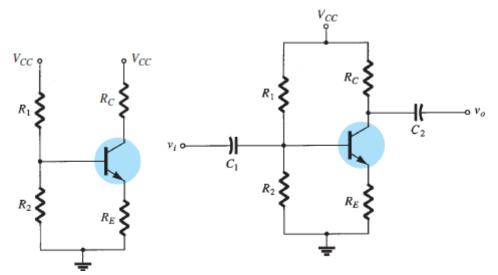

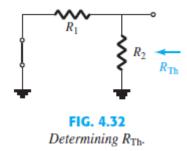

أهداف المحاضرة:

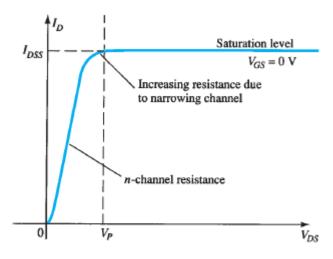

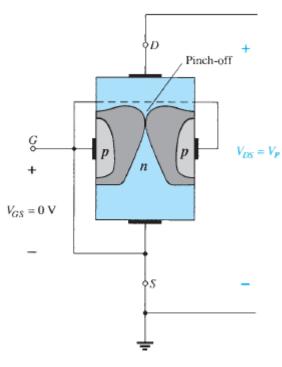

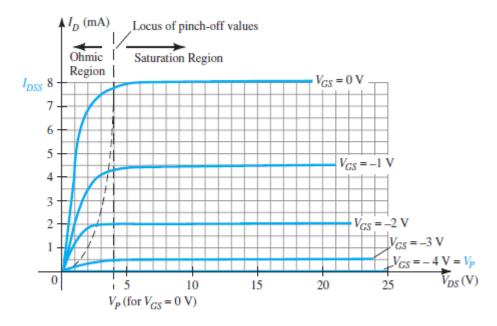

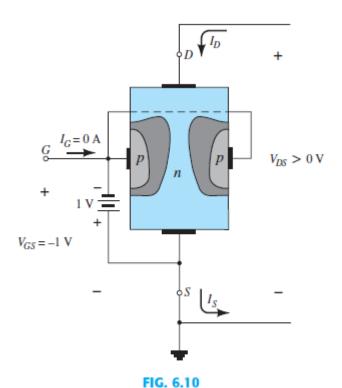

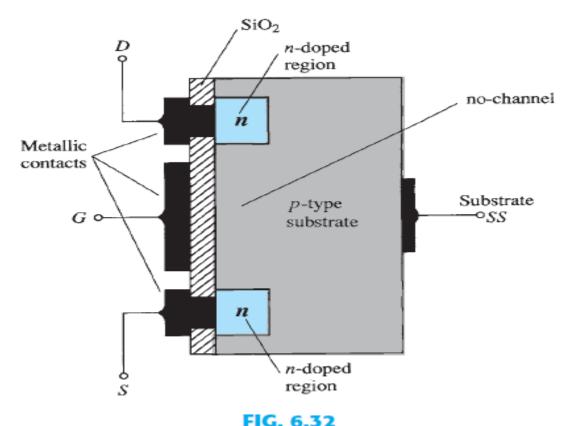

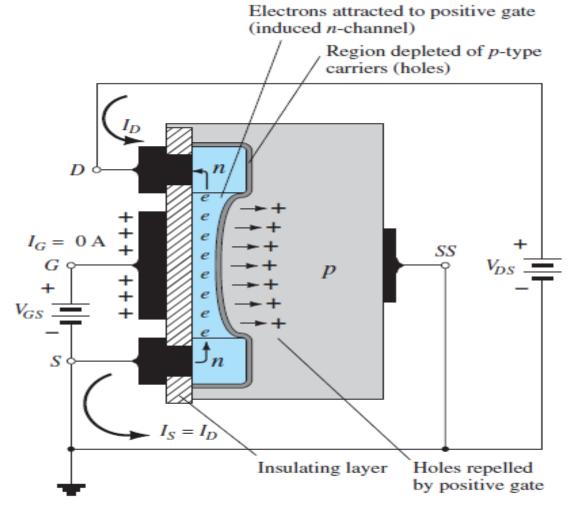

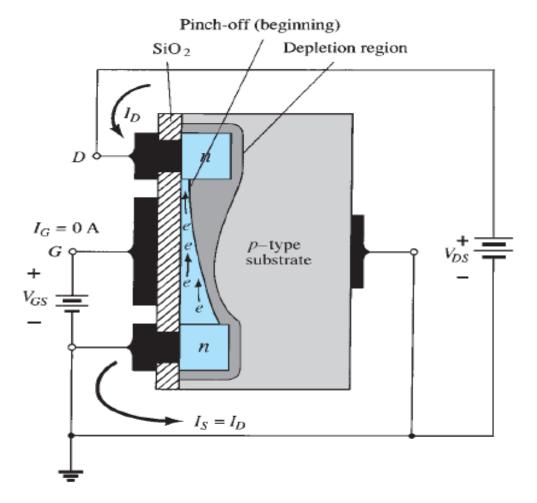

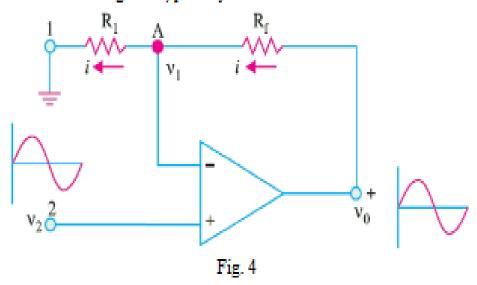

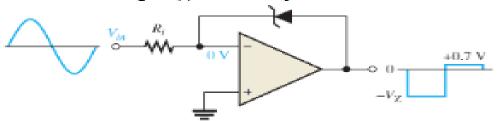

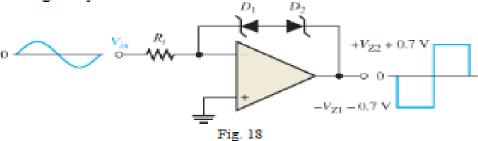

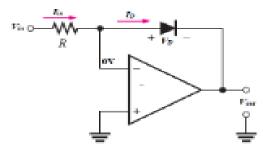

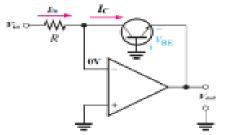

## يتوقع في نهاية الجلسة أن يكون الطالب قادراً على: